Tessent scan & ATPG(8) Debug low test coverage(低测试覆盖率的原因及debug方法)

如何利用工具debug测试覆盖率低的原因

·

如何利用工具提高测试覆盖率

low coverage 的原因

- 每个fault点的可控性和可测性;

- 部分设计规则违例会影响测试覆盖率

- 好的电路和错误的电路之间必须可以观测到不同;

- 那些没有被detect的fault 可能被分配到不需要观测的fault库, 包括AU(Atpg_untestable),UC(Uncontrolled),UO(Unobserved);

如何Debug

1.对错误进行评估,优先找覆盖率低的大的Block.

2. 判断那些分类到untested种类的错误,是否是用户干预导致的.AU,UC.UO

3.对Fualt进行逐个分析.

Assessing the Problem

使用 report_statistics 命令 查看测试覆盖率以及各fault分类的数量比例.

通过 tessent visualizer 可以可视化的去分析fault分布,以设计结构查看每一个block的测试覆盖率及fault信息.

使用 analyze_fault /p1/fpu1/U2694/A1 -stuck_at 1 -display

分析 U2694单元的A1引脚的 stuck_at 1 的问题. 看它能不能控制为0;

分析Low Coverage的原因(stuck_at)

- 你的设计没有被过度约束;

- 使用命令“report_input_constraints”找到那些被正确应用到设计中的约束。是否存在一些越是是没有必要的

- 选择性的将 C 约束 替换为 CT 约束。(C 和 CT 约束的区别? C类型会把某一点约束为一个常数,会统计到测试覆盖率之中,CT类型也会将fault 点固定为一个值,但不会分类到ATPG untestable中,所以覆盖率会有略微提高)

power pin本身就应该使用CT 约束

重新执行ATPG去评估每条约束的影响.

- 检查是否所有的时钟都被识别了。

- 使用命令"analyze_control_signals",去报告设计中的时钟和其他控制信号,包括set reset,read,write等;

- 使用 “report_clock” 去识别 ATPG 定义了哪些时钟.有没有漏接一些clock.

- 时钟门控对测试覆盖率的影响

- 时钟门控的TE端连接到 PI中的test_enable会导致低的测试覆盖率.

- 尝试使用scan_enable代替原有的 TE的连接.

- Black box对测试覆盖率的影响

- 那些没有被建模的存储器经常被识别为黑盒;

- 尝试添加输入输出的连接,去确定避开黑盒对测试覆盖率的影响.(如果你想了解black box对测试覆盖率的影响,可以通过对black box的输入输出 add_primary_inputs 和add_primary_outputs 的方式,将black box隔离)

- 确保memory 已经做了 ATPG的model;

Aborted Faults

- 工具会在超过一定的尝试次数之后,放弃fault点的pattern产生的尝试.

- 这些可能因为尝试次数不够 而不能产生pattern的点会被算到 UC和UO的类别中.

- 可以通过尝试增加 abort limit,对test coverage的影响.

- 使用report_aborted_faults 展示那些被放弃的fault点,以及他们被放弃的原因.

逐个Debug UC fualt的原因

#使用

report_faults -class class_type

report_faults -class UC

#报告完整的 UC类型的fault list

#使用

analyze_fault

#去分析指定的fault没有被detected到;

#执行fault分析,在 Tessent Visualizer中展示fault所在电路结构;

analyze_fault /p1/fpu1/U1234/Y -stuck_at 1

#使用

report_test_stimulus

#展示指定条件下的激励

-set

-write

-read

#当需要将某点控制为某个值时, 与他相关的逻辑是如何配置的.

ATPG untestable AU类型的faults

造成AU类型的原因:

- 约束(pin,cell,以及ATPG)防止在某些位置生成pattern去detect fault;

- 未被替换为扫描单元的触发器,以及不够的时序深度;

- 来自black boxes的blocking condition,其他tied或者约束值的逻辑.

debug AU类型的Faults

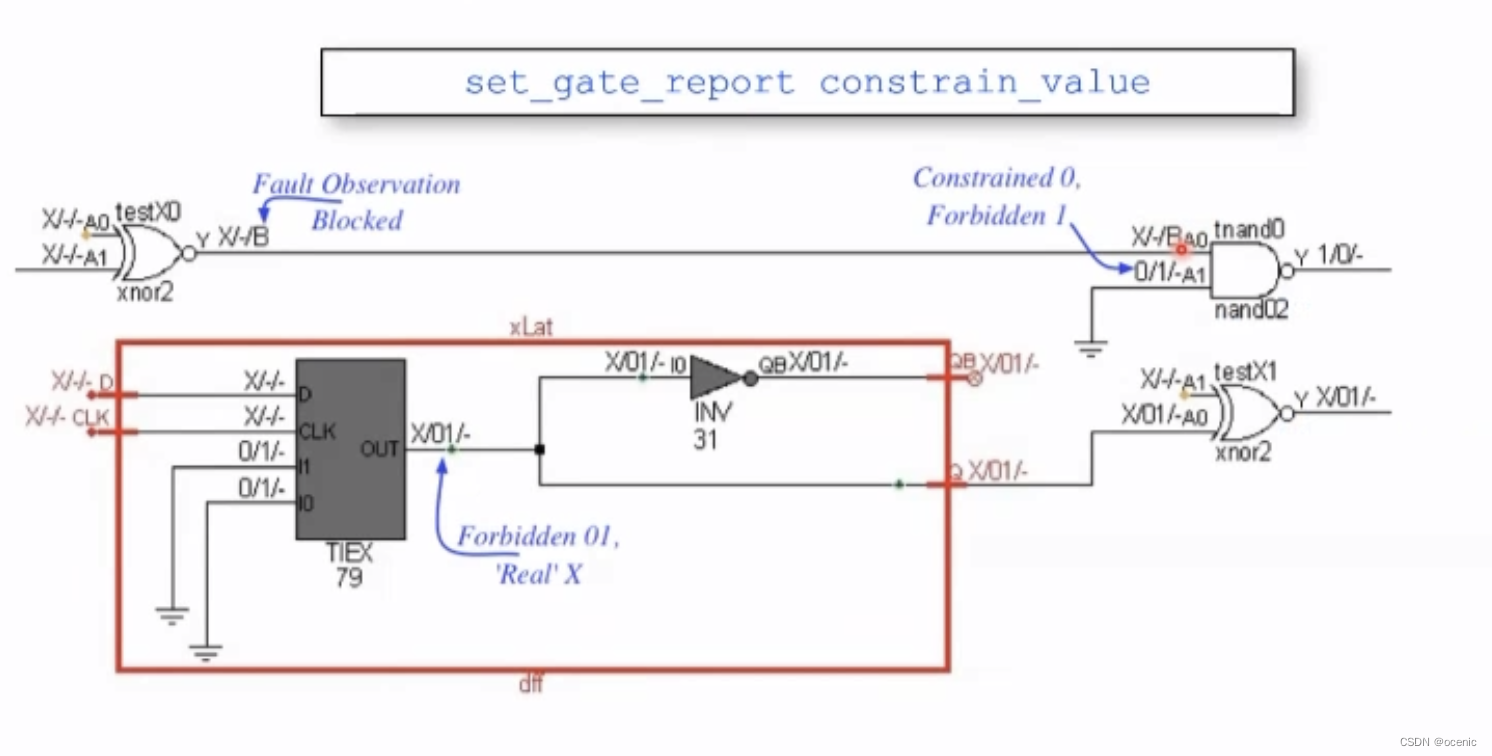

set_gate_report constrain_value

#展示约束值,forbidden值和是否被blocked

#然后

report_gate

#命令就会展示这三种值

CV/FV/B

#constrained value Forbidden Value & blocked no path to propagate fault if '-' is not blocked

#判断 AU 是否是由constrains 造成的;

如图所示, 最右侧与非门被constrained为0; forbidden1; 那么与非门的输出会恒为1; 所以前面的 xnor2 为blocking type 为B, 没有办法观测;

debug AU类型的fault,stuck-at faults;

#使用

add_atpg_constraints 1 /pin/path

#指导ATPG工具在特定位置应用一个特定值的pattern;

#如果 ATPG工具没办法设置这个约束, 使用

analyze_restriction

#去报告为什么不能设置约束;

debug AU类型的fault,Transition faults;

使用ATPG约束会创建一个pattern ,在launch和capture期间约束为一个特定的值;如果工具没有办法设置这个约束值, 使用

analyze_restriction

去报告原因;

前一级的cell constrains会影响到下一级的控制情况;

添加私有的输入点(primary input point)to help control

可以通过添加内部私有输入点的方式去控制某一点的状态;

add_primary_input /top/bypass/U10/A -pseudo_port_name my_bypass

add_input_constraints my_bypass -C0

report parallel pattern 0

#使用

set_gate_report parallel_pattern 0

# 去报告 index 为0 的parallel pattern 在电路中每个node 的值;

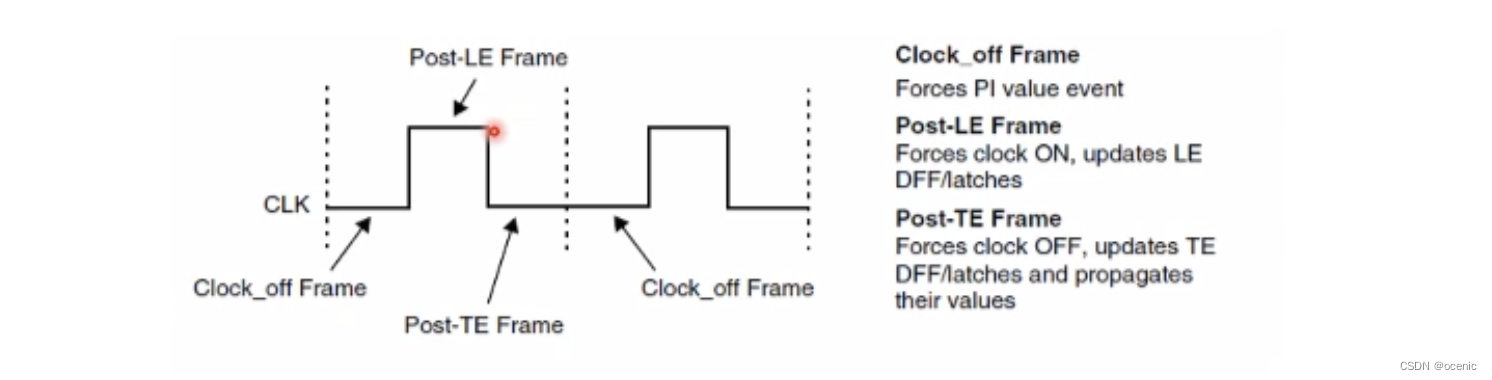

# XXX 三个值对应 clock的三个frame;

# 工具将时钟pulse 分为凸Pulse和凹pulse

# 这三个frame包括: clock_off post_LE,post_TE

# 对于边沿触发 和电平触发的时序器件,更新值的位置有所不同, 边沿触发的期间在0-1转换时触发,电平触发单元更新于clock = 1时;

#所有的单元都在相同的frame立刻更新;

set_gate_report pattern_index 4 -internal -scan_test

#去报告某一pattern的具体情况

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)