【MIPI协议 C-PHY详解】

MIPI协议中C-PHY相关知识

MIPI协议 C-PHY详解

前言

下面为MIPI协议中C-PHY相关的学习记录

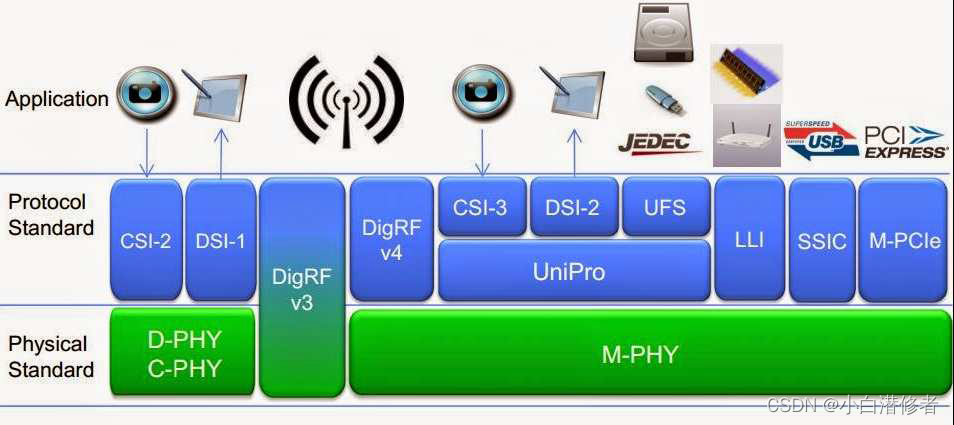

一、C-PHY介绍

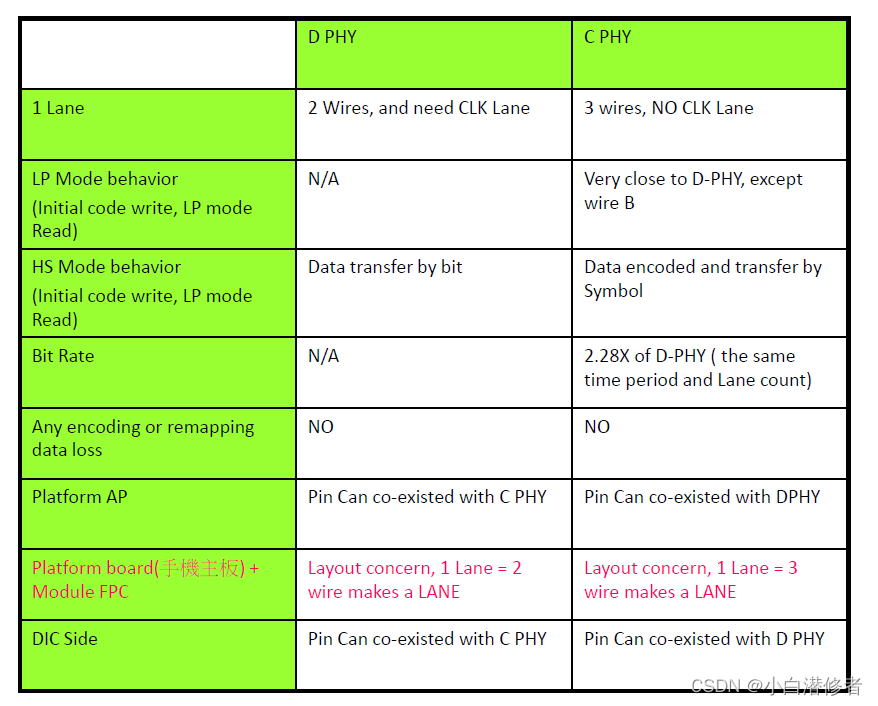

C-PHY类似于D-PHY,其逻辑层主要也是面向摄像头(CSI)、显示屏(DSI)等用途,C-PHY中的C指的是Channel-limited。C-PHY总共有3条lane,每条lane使用3根信号线,3条信号线彼此差分。C-PHY没有单独的clock,时钟信号是包含在通讯的时序中。

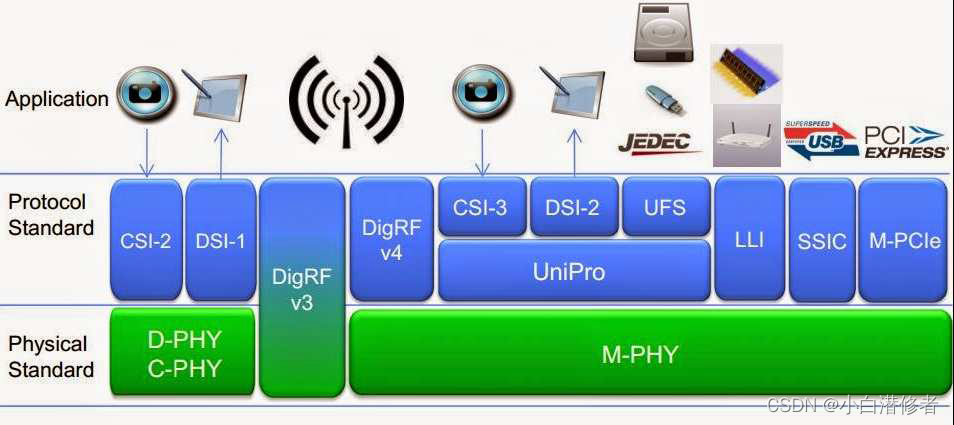

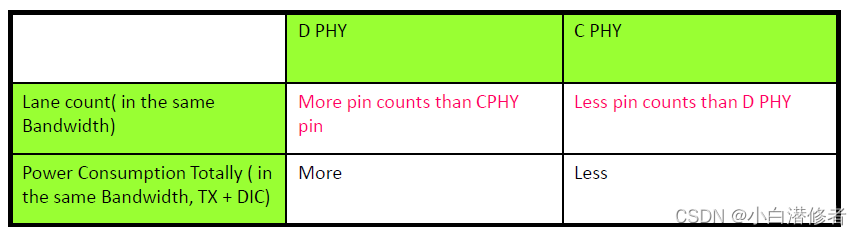

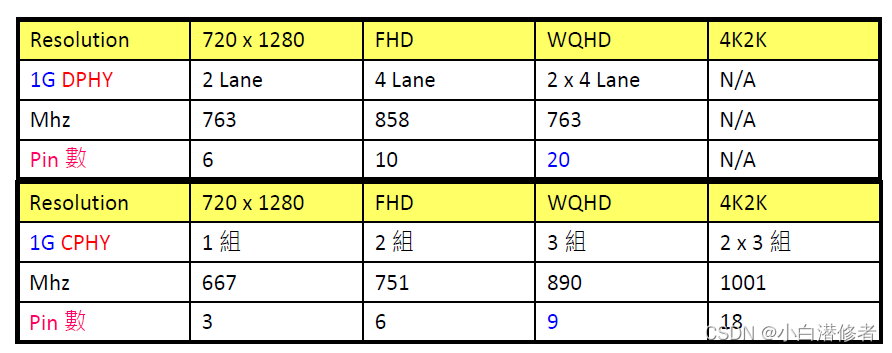

1.1 C-PHY 与 D-PHY wire的区别

1 lane with 3 wire A/B/C,each HS mode UI is one state controlled

2.single ended->3/4=375mv 1/2=250mv 1/4 = 125mv

3.Tri-State controlled for each wire,so called 3 phase D-PHY

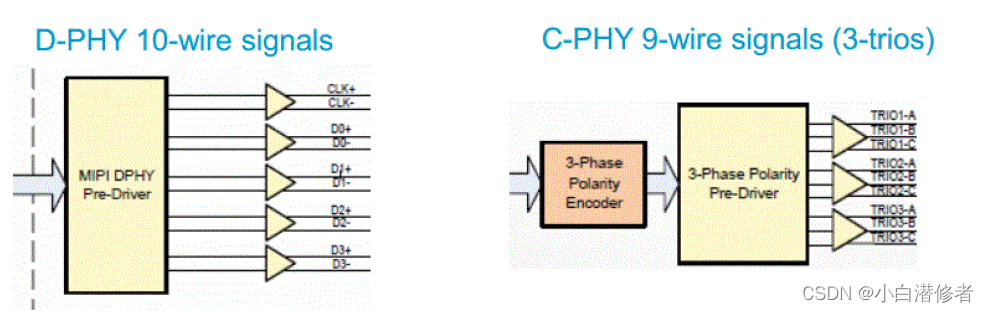

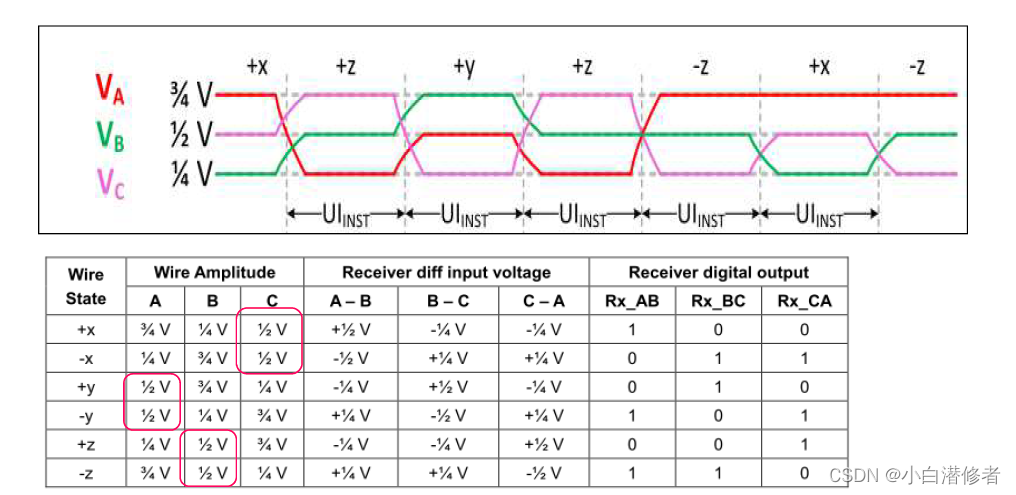

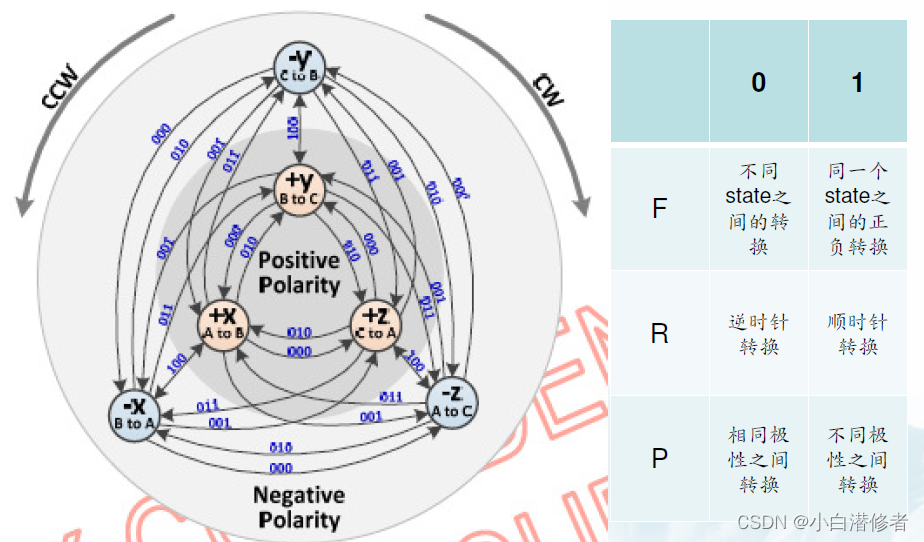

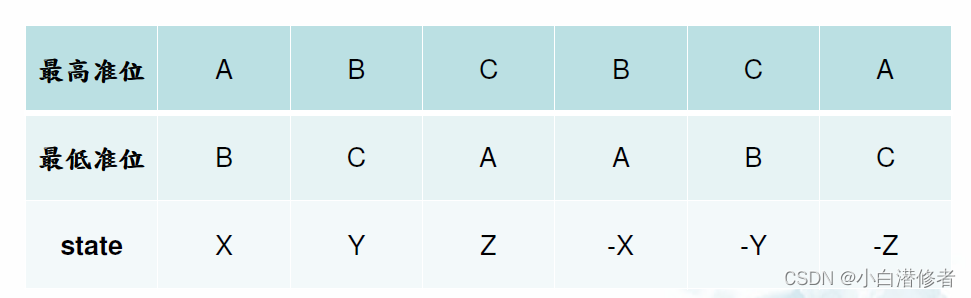

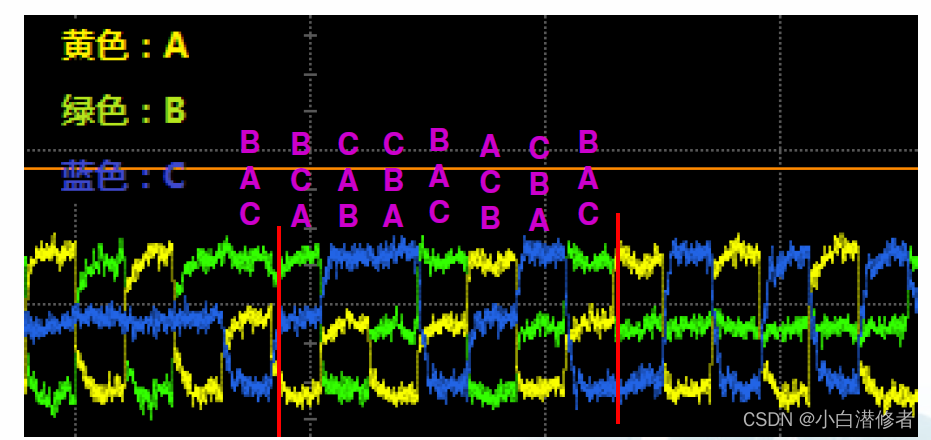

1.2 3 wire的状态(states)变化

如上所示3 wire共有6种states,对于每一种状态,下一步的变化都有5中变化状态。

example:+y can switch (-y -x +x -z +z)

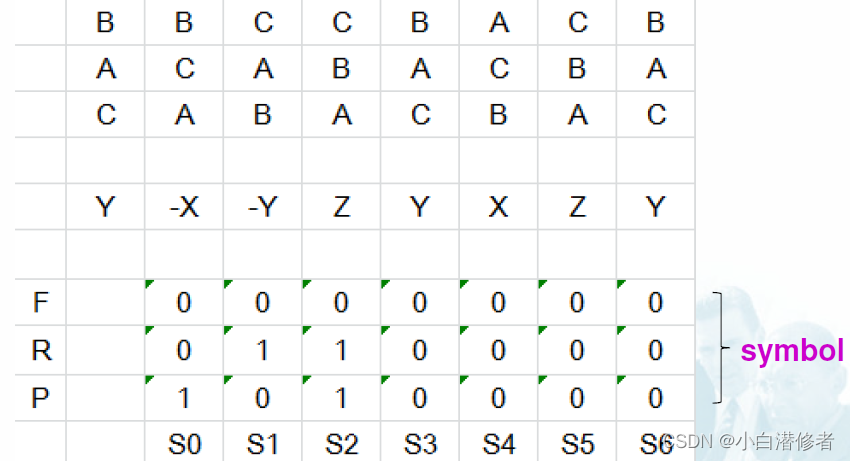

注意:将states 转成 symbol的记忆方法:只需记住x y z 的位置

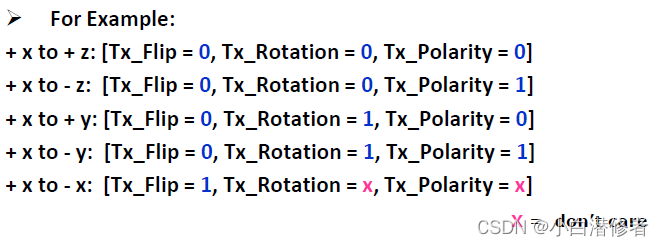

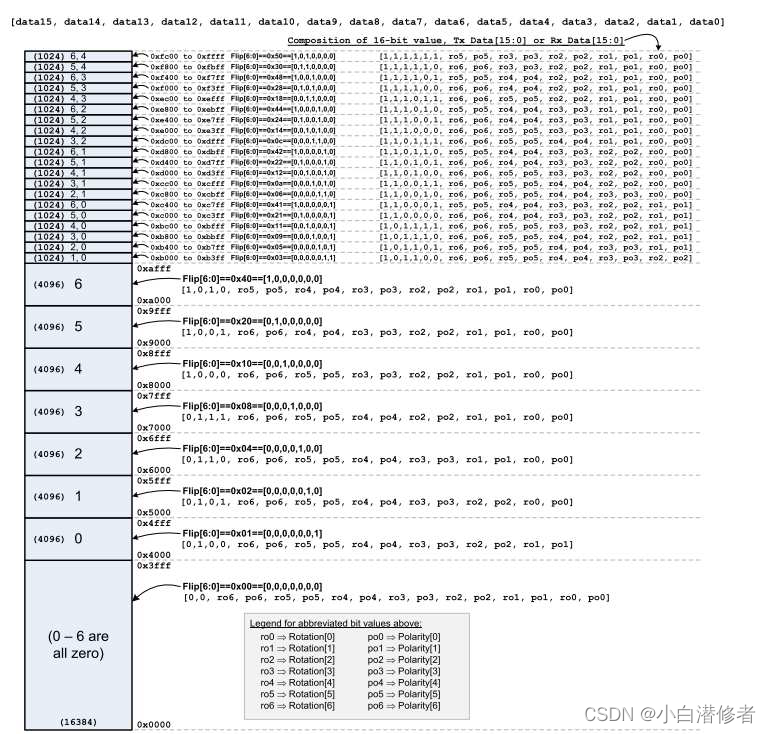

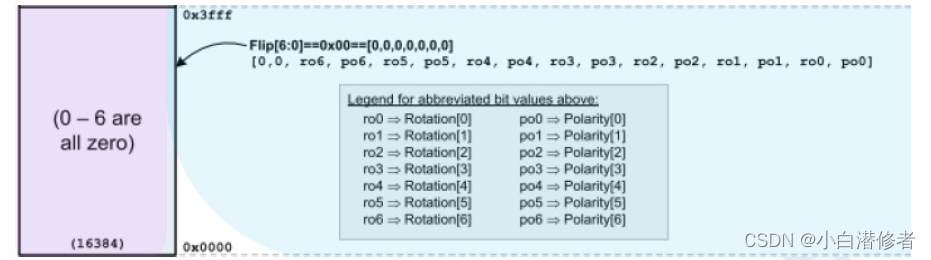

1.3 C-PHY Data Mapping Between 7 Symbols and a 16-Bit Data

我们可以通过mappIng映射表将7 symbols和16-bit data之间的对应关系查看出来

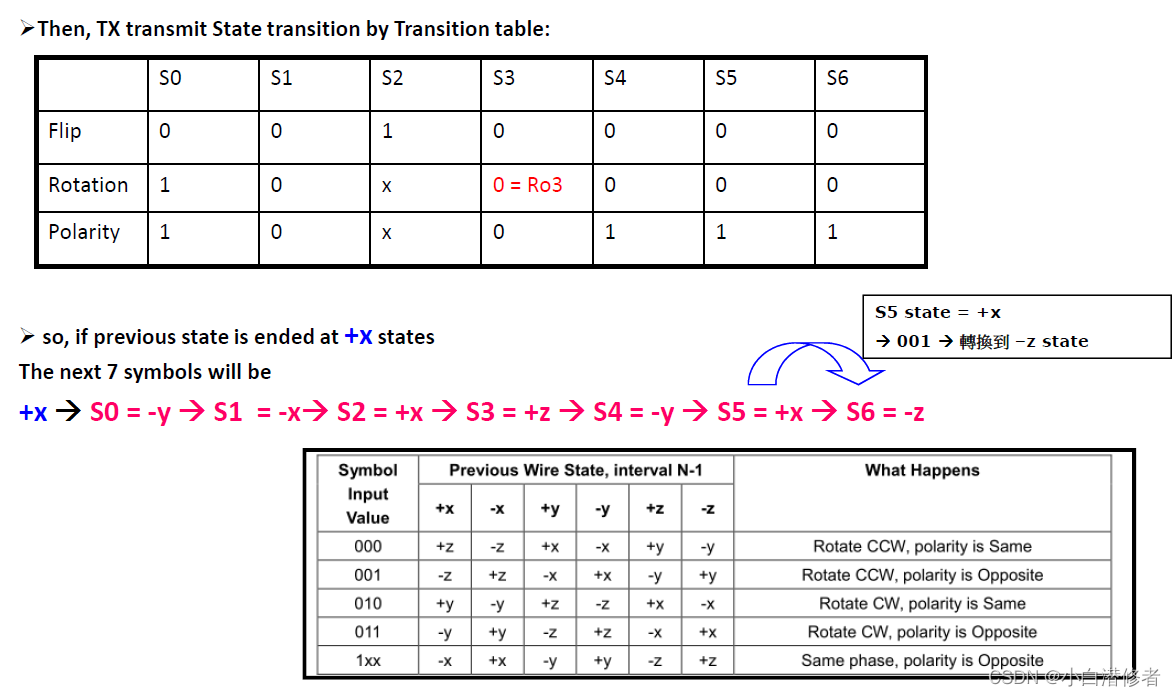

For example, TX need to send TX_Data[15:0] = 0x6543 to DIC side

1.First, look up the mapping table, 0x6543 is between 0x6000 to 0x6FFF

2.By mapping table

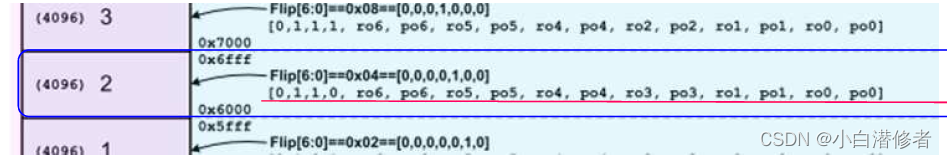

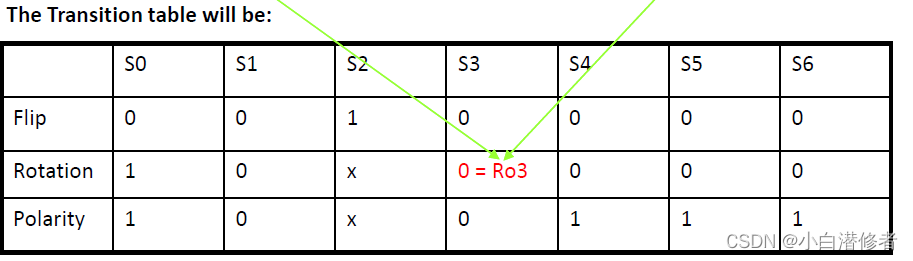

0x6543 = 0110 0101 0100 0011 = [0,1,1,0, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro1, po1, ro0, po0]

TX need to send TX_Data[15:0] = 0x6543 to DIC side

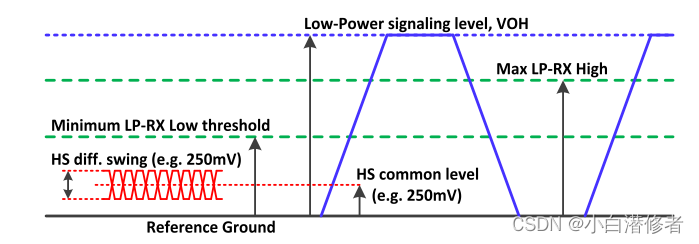

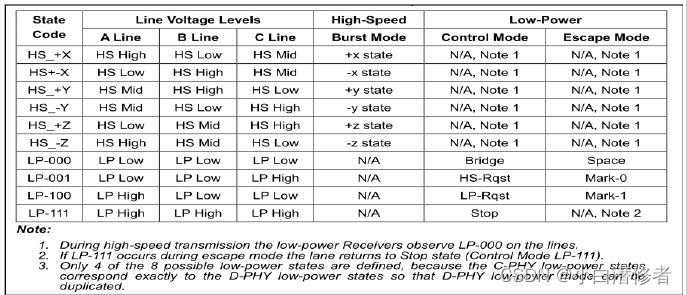

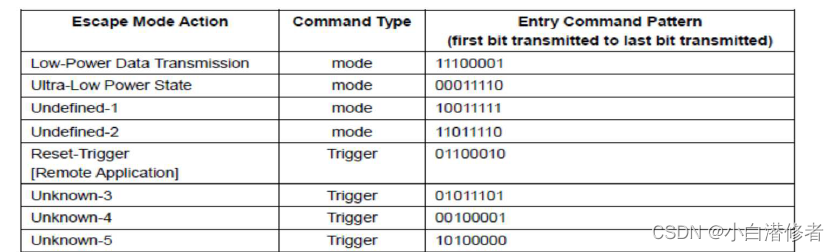

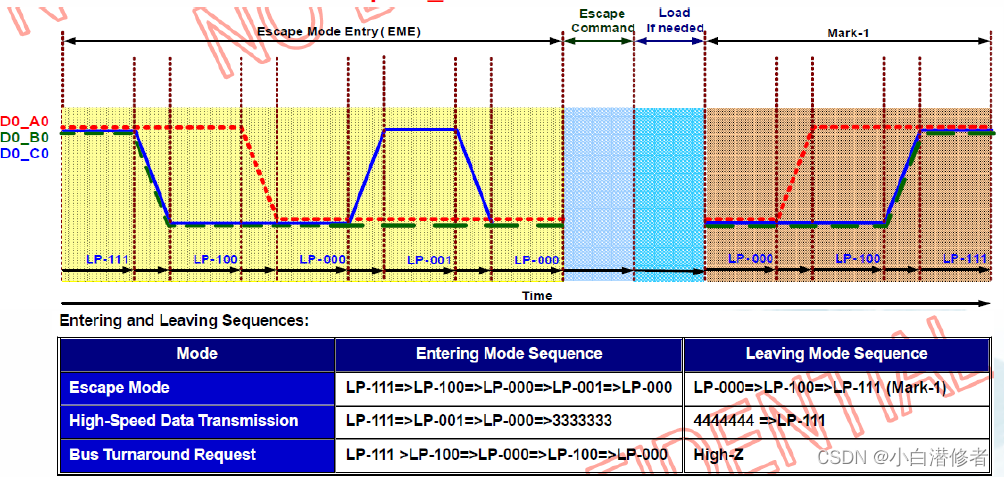

1.3 C-PHY Lane States and Line Levels ~ LP Mode

LP Mode C-PHY和D-PHY很相像,但是C-PHY 1Lane有3条wire,A/B/C,wire B will not do transition in the LP mode Escape mode

C-PHY和D-PHY

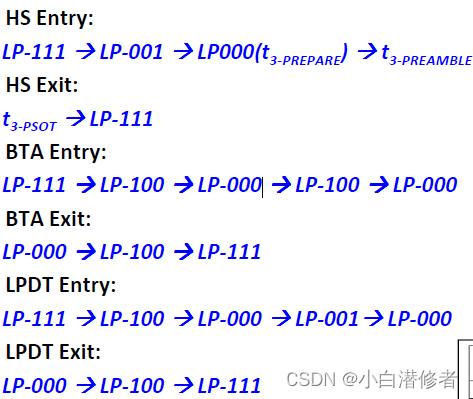

二、C-PHY LP Package Format

C-PHYd的LPDT Protocol与D-PHY基本完全一致:

Lane0-A —>D0+

Lane0-C---->D0-

Lane0B----->keep LP_Low(不关心)

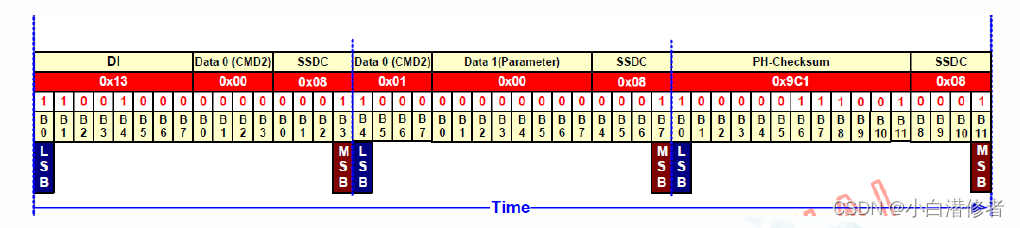

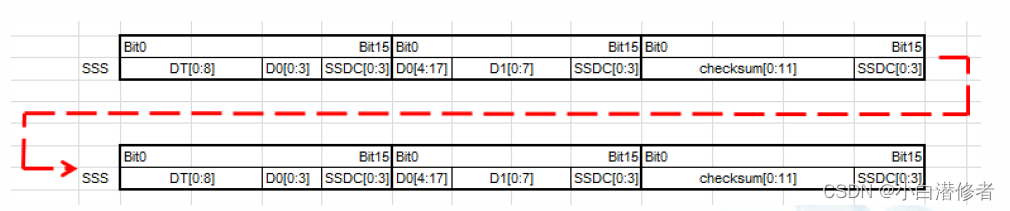

2.1 C-PHY HS Short package Format

C-PHY HS package新增SSDC(包括short和long package)

SSDC:

Symbol Slip Detection Code,只在short package以及long package的PH中出现,固定为8(1000)

C-PHY HS Short package 会连续送两次,如果其中一次出错,会报error,但是数据会采用正确的那次资料,如果两次资料都错,就报error并直接忽略

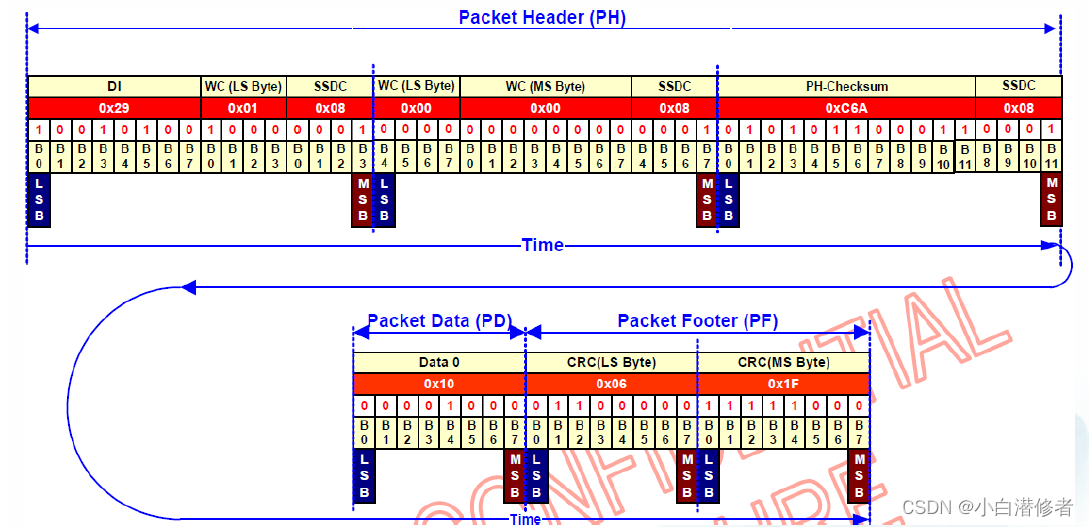

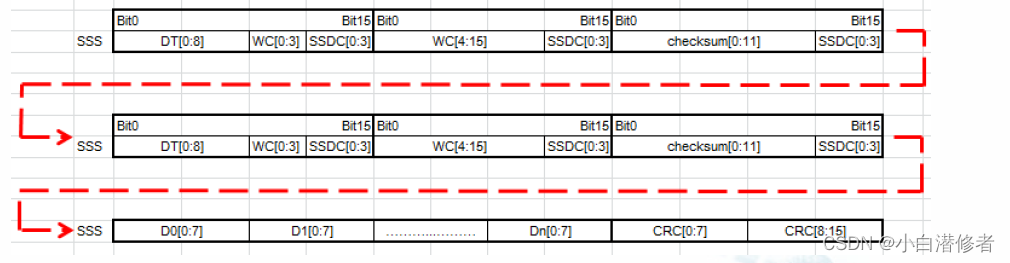

2.2 C-PHY HS Long package Format

long Package 和 short Package 发送相同都需要连续发送两次

host 在传输数据时,会对数据进行二次编码:

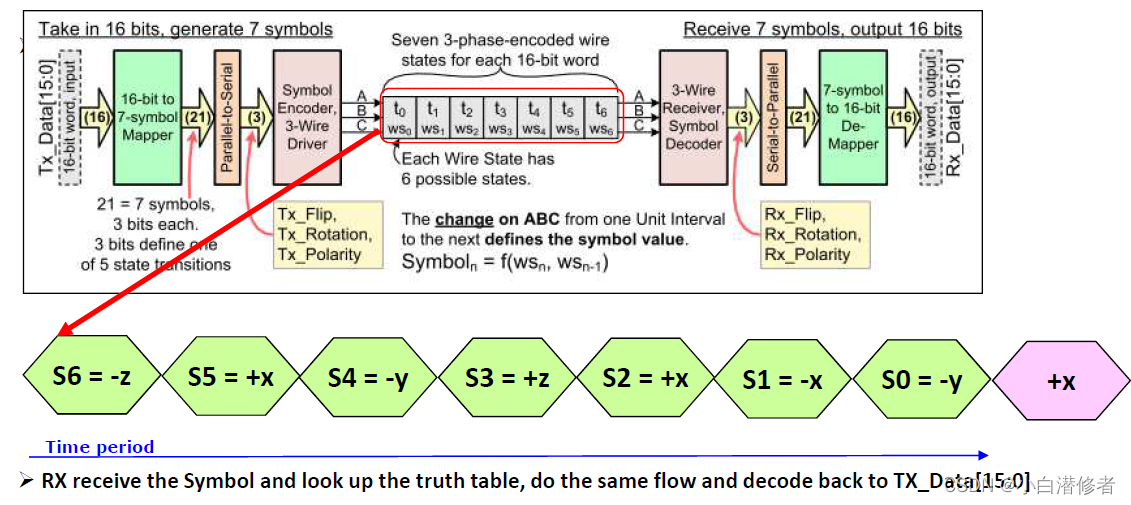

1.将16bit数据转成7个symbol

2.将7个symbol转成对应的状态(+x -x +y -y +z -x)

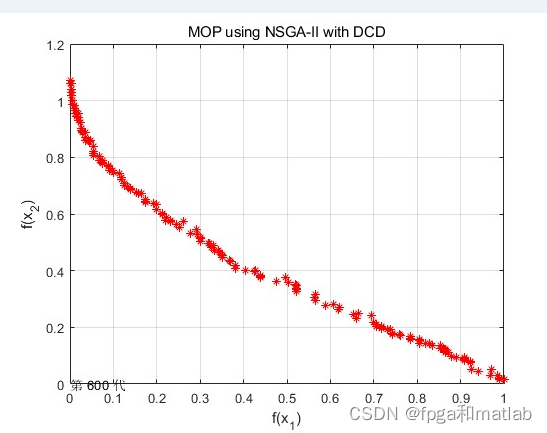

C-PHY的传输效率是D-PHY的:16 / 7 = 2.28倍

对于DIC与host则相反,但需要进行二次编码:

1.将(+x -x +y -y +z -x)转成7个symbol

将7个symbol转成16bit data

C-PHY状态(state)的简单记忆规则:

- 忽略中间准位,只看最高准位和最低准位;

- 以最高和最低来识别state

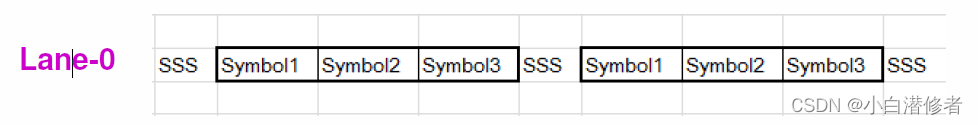

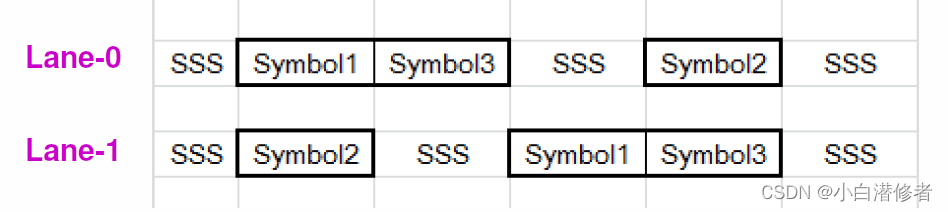

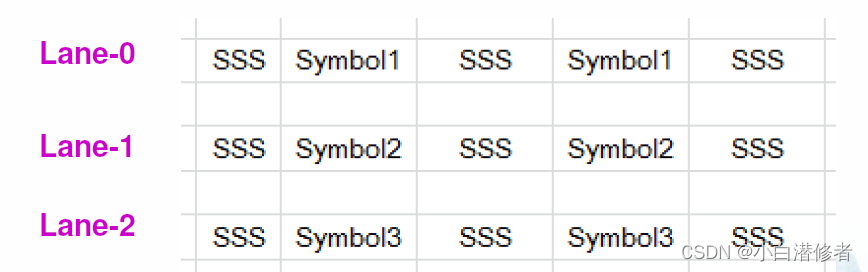

三、C-PHY Lane Management

1-Lane

2-lane

3-lane

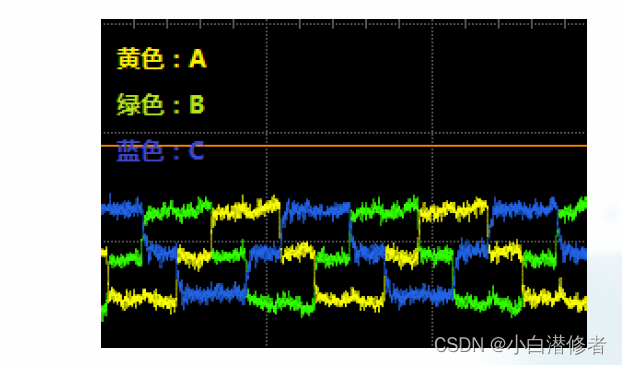

四、C-PHY package解析计算

1.由波形图求出状态变化

2.在这步中我们可以只关注最高标准位和最低标准位,然后根据上面states的计算规则得出下面的F R P symbol的各值

3.Flip = 0000000,查表得到数据在block0中

4.参考表中数据 0000 0000 0011 1001 =0x0039

SSDC:Symbol Slip Detection Code,只在short package以及longpackage的PH中出现,固定为8(1000)

这个案例中的波形是异常的,异常点为SSDC=0,

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)