DDR3/4 内存模组(SIMM DIMM RIMM ,SO-DIMM UDIMM RDIMM LRDIMM区别)

DDR3/4 内存模组Overview0.内存芯片、内存颗粒DDR3 SDRAM1.常见的DIMM分类及区别1.1 内存模组尺寸分类1.2 内存模组功能分类如何改变文本的样式插入链接与图片如何插入一段漂亮的代码片生成一个适合你的列表创建一个表格设定内容居中、居左、居右SmartyPants创建一个自定义列表如何创建一个注脚注释也是必不可少的KaTeX数学公式新的甘特图功能,丰富你的文章UML 图表

DDR3/4 内存模组

Overview

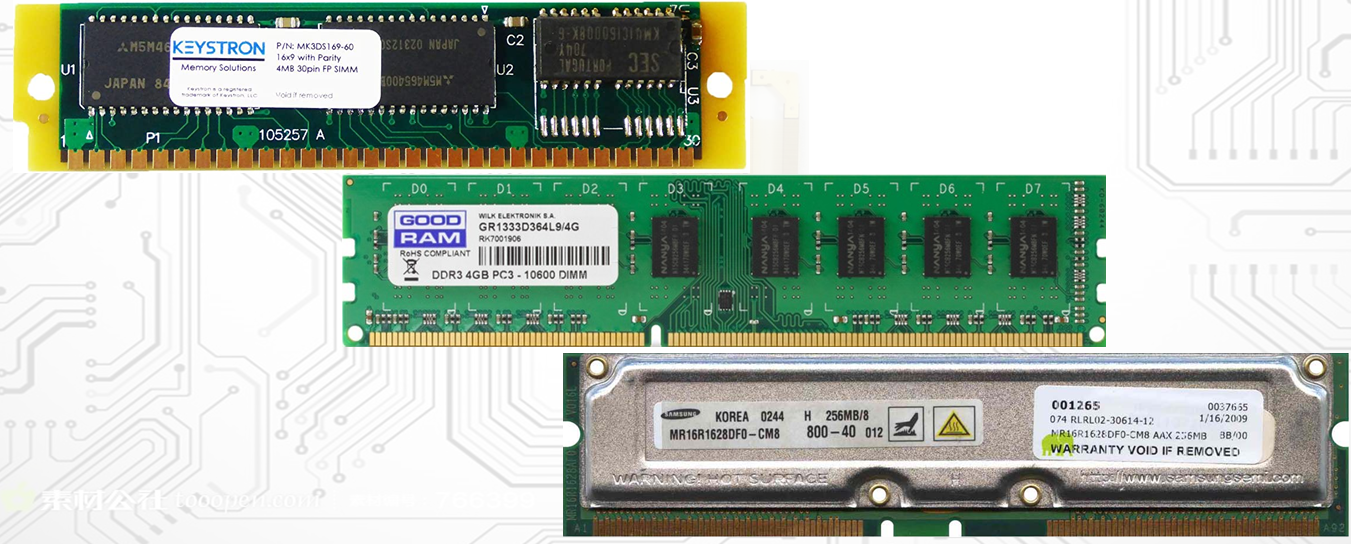

内存模组是内存在PC系统中的最终体现形式,内存模组接口类型主要有SIMM(Single Inline Memory Module,单列直插内存模块)、DIMM(Dual Inline Memory Module,双列直插内存模块)、RIMM(Rambus Inline Memory Module,内联内存模块)。其中SIMM就是一种两侧金手指都提供相同信号的内存结构,它多用于早期的FPM和EDDDRAM,在内存发展进入SDRAM时代后,SIMM逐渐被DIMM技术取代;DIMM与SIMM相当类似,不同的只是DIMM的金手指两端不像SIMM那样是互通的,它们各自独立传输信号,因此可以满足更多数据信号的传送需要;RIMM模组由RDRAM芯片构成,是金士顿技术公司开发的、是一种比早期的DIMM模组占用更少空间的记忆体模组,RIMM通常认为代表的是Rambus专用记忆体模组。以下介绍应用最多的DIMM接口类型内存模组。

图1 DDR3/4 内存模组 SIMM/DIMM/RIMM(从左至右)

0.内存芯片、内存颗粒DDR3 SDRAM

首先来了解下内存模组上芯片的的结构和关键管脚信息,内存芯片DDR SDRAM 包括非数据类型线如A[0:15]\RAS\CAS\WE\BA等;数据线DQ;数据选通线DQS;电源信号等:

图 2 内存芯片pin 结构

1.常见的DIMM分类及区别

图 3 DIMM 分类

Unbuffered DIMM:指没有经过缓冲,定位在桌面市场,是市面上最常见的[内存]模组。

早期的SDR[内存]模组,有Buffered类型的,现在已经很少见了。Buffered[内存]模组和后面提到的Registered[内存]模组并不是同一个东西,Buffered[内存]模组是将地址和控制信号等经过缓冲器,没有做任何时序调整(缓冲器延迟是有的);而Registered[内存]模组则对地址和控制信号等进行寄存,在下一个时钟到来时再触发输出。而Unbuffered DIMM是不经过缓冲直接与颗粒相连;(这里原图书写有误,感谢读者地指出谢谢)

1.1 内存模组尺寸分类

- STANDARD DIMM

Standard :标准宽型,【台式机,服务器】常规类型,默认类型 -288Pin , 0.85mm Pitch

图 4 Standard DIMM

- VLP窄型

VLP:Very Low Profile【台式机、服务器】,矮小类型-288pin ,0.85mm pitch

图 5 VLP DIMM - SO 小型

SO: Small Outline小型【笔记本、工控机、微控器】

图 6 SO DIMM - MINI 微型

迷你型【很少见】-288Pin,0.5mm Pitch

图 7 MINI DIMM

1.2 内存模组功能分类

UDIMM无ECC

以X16内存芯片为例,DQ[15:0],颗粒数4PCS = 64/16【无ECC】;

ECC(Error Correcting Code):增加8bit纠错码,提高数据可靠性;

U(Unbuffered):CPU与内存条上的芯片直接连接,非数据线/数据线不使用Buffer

图8 UDIMM 无ECC

UDIMM有ECC

以X16内存芯片为例,DQ[15:0],颗粒数4PCS = 64/16【无ECC】,颗粒数5PCS ~ 72/16【有ECC】;

ECC(Error Correcting Code):增加8bit纠错码,提高数据可靠性;

U(Unbuffered):CPU与内存条上的芯片直接连接,非数据线/数据线不使用Buffer

图9 UDIMM 有ECC

RDIMM

R:Registered 【一般带ECC功能】CPU非数据线经过Buffer后连接到内存芯片,增加驱动能力;

图10 RDIMM

UDIMM与RDIMM区别

现在再回头看看UDIMM,就很明白了。它对比RDIMM关键就少了寄存器,但为什么不称之为Unregistered-DIMM呢?其实,==Buffered与Registered是RDIMM的两种工作模式,前者在RDIMM上并不常用,它是以时钟异步方式工作的,输出信号的再驱动不与时钟同步,Registered模式下输入信号的再驱动则与时钟同步。==显然,Buffered模式下的性能要更低一些。不过,从原理上讲Registered模式也是一种缓冲操作,只是与时钟同步而已。在SDRAM的RDIMM上,Buffered与Registered模式通过REGE信号控制,但到了DDRSDRAM-DIMM时代,可能由于性能的原因Buffered模式被取消了。在UDIMM上,没有寄存器也就没了这个Buffer,但它仍可具备ECC功能。这里需要强调的是,ECC与Registered是两码事,前者是在逻辑上保证数据的安全,后者是在物理上保证内存系统的稳定工作。

图11 DDR内存模组结构图

为了保证内存工作时钟的稳定,RDIMM上还要有一颗PLL对时钟信号对主板发来的时钟信号进行跟踪/锁定。

LRDIMM

== R:Registered 【一般带ECC功能】CPU飞鼠极限经过Buffer后连接到内存芯片,增加驱动能力。==

LR:Load Reduced 【一般带ECC功能】CPU非数据线经过Buffer后连接到内存芯片,增加驱动能力,CPU数据线经过Buffer后与内存芯片连接,增加驱动能力;

图12 LRDIMM

1.3内存种类(概念区分)

命名规则:尺寸+功能+DIMM

图13 命名规则

2.SPD-串行检测 详解

SPD是SERIAL PEESENCE DETECT的缩写,中文的意思是模组存在的串行检测。

内存条上存在一个EEPROM存储芯片(The Serial Presence Detect, SPD),容量通常为128B(RDIMM)或256B(UDIMM),用于存储内存条的一些基础信息,如Rank数量、电压、行地址/列地址数量、位宽、各种主要操作时序(CL、tRCD、tRP)。主板需要这些信息进行正确的配置,一边正常使用内存条。

也即是通过IIC串行接口的EEPROM对内存插槽中的模组存在的信息检查。这样模组的相关信息必须记录在EEPROM中。SPD的信息由模组生产商写入,主要用来协助Controller精确调整内存的物理/时序参数,避免人为出现调教错误而引起故障。

图14 SPD

2.1 DDR3 SDRAM Serial Presence-Detect Table

SPD对于内存技术而言是一组关于内存模组的配置信息。如内存频率、电压、行地址/列地址数量、位宽等,将这些信息烧录进一个eeprom(电可擦可编程只读存储器)电子原件中,方便CPU直接读取的内存相关数据信息。

另外,这个概念也是针对CPU可支持的内存频率而言的,主要用途就是方便或者说协助CPU(具体应为整合进CPU的北桥芯片)精确读取和调整内存的物理/时序参数,以达到最佳的使用效果。

内存spd技术就是将内存的相关参数烧录进eeprom(电可擦可编程只读存储器)电子原件中,方便BIOS读取,比如,当主板上插有新旧两条容量一致的内存时,为保证系统稳定,主板BIOS无法对两条内存的频率分别调整时,可以把性能弱的SPD刷到强的那条内存上,以提高系统稳定性。

SPD芯片是一块可擦写的存储器,里面记录了该内存的许多重要信息:一类是基本参数,如频率、容量、时序等;另一类则是内存模块序列号、制造商代码等信息。SPD信息一般都是在出厂前,由厂商根据内存的实际性能写入到SPD芯片中。上图为影驰HOF EXTREME DDR4 内存的SPD芯片。

所以,正是有了它的存在,主板中的芯片组才得以将里面的SPD信息读取出来,并根据这些参数来自动配置相应的运行方式,从而让内存条发挥出相应的性能。

以存储芯片中各字节存储的信息如下表所示。

续

3.SO-DIMM设计要点

1.在进行电路设计前,确定芯片配置DDR时,器件手册上适配的器件型号(参考sprabi1c-DDR3 Design Requirements for KeyStone Devices);

2.电源设计时,需要考虑电压电流以及上电时序是否满足要求(TPS51200);

3.ZQ校正功能,加240欧姆的电阻到地;

4.注意PCB layout.

(严格控制阻抗、电源、数据线等长、地址线等长、切勿跨分割)

5.参考电源VREFCA可以使用电源芯片提供,也可以采用电阻分压方式得到。

6.通用配置

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)