国产DSP FT-M6678开发-Cache控制器

FT-M6678 C6678 开发 Cache说明

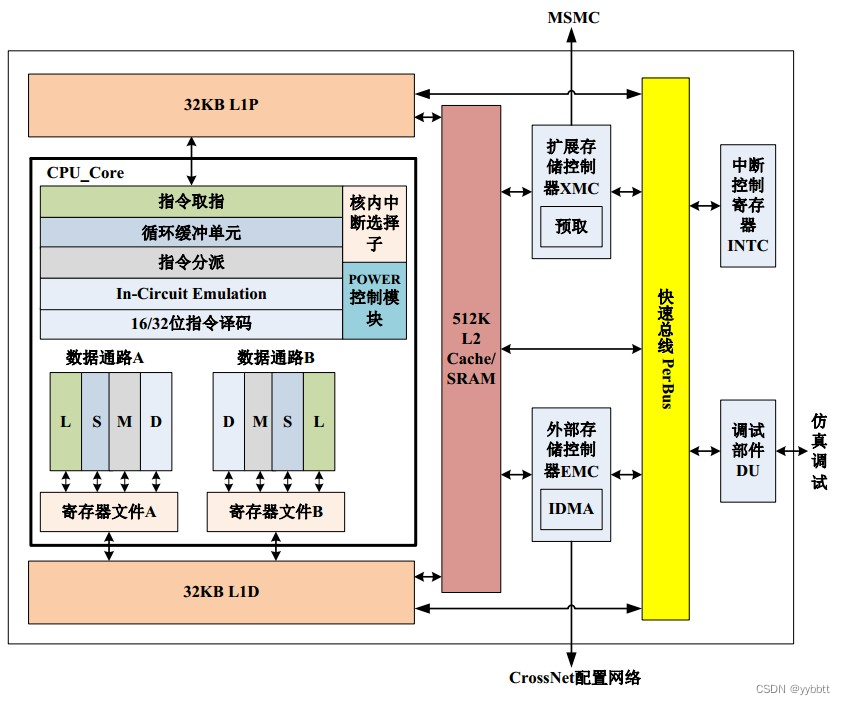

FT-M6678与TI C6678一致,在DSP内部存在两级核内存储器,其中一级程序存储控制器(L1P),一级数据存储控制器 (L1D),二级存储控制器 (L2),其中 L2 为 512KB, L1 分为 L1P 和 L1D,容量均为 32KB。

L1P:

L1P 主要作用是负责直接向 CPU 提供指令,根据取指单元计算出的 PC值取回相应的指令包。

对于L1P来说,最大32KB,软件可配置SRAM和Cache的比例:

1. L1P支持 2 种 flush 操作:全局作废、块作废;L1P Cache 的一致性由软件维护;

2. 支持Freeze模式:可以保护 Cache 中已有的关键程序,在 Freeze 模式下 L1P 不会分配新的数据行,不发生替换。 Freeze 模式对正常的 flush 操作无影响;

3. 支持 IDMA/EMC 访问,可以从 L1P SRAM 快速导入和导出程序;

4. 支持内置带宽管理机制和存储保护机制;

L1D:

L1D 是最靠近 CPU 的数据存储体,其工作频率与 CPU 保持一致。

1. L1D 可配置 SRAM/Cache 比例, 当程序修改 CFG 寄存器改变 L1D 配置模式时由硬件自动写回并作废 Cache 中已有的数据。利用 DMA 可以从 L1D SRAM 快速导入和导出数据;

2. 支持 6 种 Cache Flush 操作: 3 种块操作——块写回、块无效、块写回并无效; 3 种全局操作——L1D 全局写回、全无效、全写回并无效。 当程序进行 L2 flush 操作时, L1将进行镜像操作。

3. 支持 Freeze Mode。可以保护 Cache 中已有的重要数据,当读缺失发生时, L1D 既不会发生替换,也不会分配新数据行。 Freeze 模式对正常的 flush 操作无影响。

4. 支持 IDMA/EMC 访问,可以从 L1D SRAM 快速导入和导出数据。

L2:

L2 Cache 作为 L1D 和 L1P 公用的下一级存储器, 既可以放程序也可以放数据, 总容量为 512KB。其中 L2 SRAM 内的数据可以在 L1D/L1P Cache 中存在副本,并且支持 EMC/IDMA 的访问。

1. L2 可配置 SRAM/Cache 比例, 当修改 CFG 寄存器 Mode 域改变 L2 配置模式时由硬件自动写回并作废 Cache 中已有的数据;

2. 支持 6 种 Cache Flush 操作: 3 种块操作——块写回、块无效、块写回并无效; 3 种全局操作——全局写回、全局作废、全局写回并作废。 当程序进

行 L2 flush 操作时, L1 将进行镜像操作;

3. 支持 Freeze Mode。可以保护 Cache 中已有的重要数据, L2 在 Freeze 模式下不会发生替换,也不会分配新数据行。 Freeze 模式对正常的 flush 操作无影响;

4. 可缓存性与可预取性控制;

5. 支持存储保护和带宽管理机制。

一致性维护

下面就是编程时很重要的地方了,一致性维护问题:

M66x 提供了两种方式维护一致性,一种是硬件自动维护(仅维护 L2SRAM 与 L1D Cache 之间的一致性),一种是软件干预的手动 flush, 即:

1. 硬件自动维护 CorePac 内 L2 SRAM 与 L1D Cache 之间的一致性;

2. 硬件不维护 CorePac 的 L2 SRAM 与 L1P Cache 之间的一致性;

3. 硬件不维护外存数据与 L1 或 L2 Cache 中的副本之间的一致性。

由文档可以看出L2SRAM和L1D Cache之间的一致性是硬件维护的,也就是不需要执行FLUSH操作就可以实现数据一致性维护。

Flush 操作

L1 和 L2 支持多种 flush 操作,按操作的范围可以将其大致分为两类:

1. 块 flush 操作——简称块/局部操作,它针对一个特定地址范围内的数据进行的操作;

2. 全局 flush 操作——简称全局操作,它是对 Cache 中所有数据进行的操作。

从操作的类型来看, L1 和 L2 支持以下 3 类操作:

1. 作废(Invalidate, I) ——直接将缓存块作废,数据直接丢弃;

2. 写回(Writeback, W) ——将脏数据写回,数据仍保留在 Cache 中;

3. 写回作废(Writeback-Invalidation, WI)——将脏数据写回,数据不保留在 Cache中。

在进行 Cache flush 时,L1 会跟随 L2 做镜像操作,即如果 L2 进行了某种 flush操作, L1P 和 L1D 将自动进行相应的 flush 操作。举例: L2 进行全局 WI 操作,那么 L1P 和 L1D 将自动进行全局 WI 操作(由于 L1P 中不可能有脏数据,这里相当于 L1P 进行全局 I 操作)。

全局FLUSH

程序通过向相应的全局 flush 控制寄存器(L1PI, L1DI, L1DW, L1DWI, L2I,L2W, L2WI)中写入 1 来启动对应的全局 flush,操作完成之后硬件自动清零,程序可以通过以下两种方式来确定 flush 操作是否完成:

1. 检测全局控制寄存器的值是否为 0;

2. 在写全局控制寄存器后加 MFENCE 指令。

由于在进行 Cache flush 时, L1 会跟随 L2 做镜像操作,下表列出了 L2 支持的全局 flush 命令及其对 L1 的影响。

块FLUSH

块 flush 操作与全局 flush 操作具有相似的功能,区别在于块操作的对象仅是针对一定范围内的数据块,数据块由基地址和字数这一对寄存器指定。

块 flush 操作的应用过程如下:

1. 向 XXBAR 寄存器写入起始基地址;

2. 向 XXWC 寄存器写入计数值;

3. 通过以下两种方式来等待块操作的完成:

a) 采用 MFENCE 指令(推荐);

b) 循环检测 XXWC 寄存器的计数值,直至 XXWC 的值变为零。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)