FPGA采集AD7606数据UDP网络传输 提供工程源码和技术支持 附带上位机接收软件

FPGA采集AD7606数据UDP网络传输 提供工程源码和技术支持 附带上位机接收软件本设计使用UDP传输FPGA采集的AD7606数据,上位机通过接收网口的 UDP 数据包,将AD7606的波形数据数据显示在电脑上。我们可以用更加直观的方式观察波形,是一个数字示波器雏形,并且可以保存 ADC 数据。

目录

1、前言

目前网上的fpga实现udp基本生态如下:

1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是废物,在实际项目中不会用这样的代码,试想,多机互联,出现了问题,你的网卡都不带ping功能,连基本的问题排查机制都不具备,这样的代码谁敢用?

2:带ping功能的udp收发器,代码优秀也好用,但基本不开源,不会提供源码给你,这样的代码也有不足,那就是出了问题不知道怎么排查,毕竟你没有源码,无可奈何;

3:使用了Xilinx的三速网IP实现,这样的代码也很优秀,但还是那个问题,没有源码,且三速网IP需要licence,官方提供的licence有效期只有120天,其实三速网IP仅仅实现了rgmii到gmii再到axis的转换,完全可以不用这个ip;

本设计使用的UDP方案使用Micrel公司的KSZ9031RNX作为网络PHY芯片,使用verilog代码设计UDP协议,并带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;

本设计使用UDP传输FPGA采集的AD7606数据,上位机通过接收网口的 UDP 数据包,将AD7606的波形数据数据显示在电脑上。我们可以用更加直观的方式观察波形,是一个数字示波器雏形,并且可以保存 ADC 数据。

2、我这里已有的UDP方案

目前我这里有如下几种UDP方案和应用实例:

我的博客主页有个FPGA以太网通信专栏,专栏是免费的,里面有很多FPGA实现的UDP应用,对网络通信有需求的兄弟可以去看看:直接点击前往

3、AD7606采集详解

AD7606输出有串行和并行两种模式,要想玩儿转AD7606,首先要读懂数据手册,基于数据手册设计接口时许,我这里既有串行模式也有并行模式的采集,之前已经写过一篇文章详细讲解了,兄弟们可以先回头看看我那篇文章,打打基础:直接点击前往

4、UDP设计方案

本实验以千兆以太网 RGMII 通信为例来设计 verilog 程序,UDP分为两部分,分别为发送和接收,实现了 动态ARP,UDP,Ping 和10/100/1000M网速自动协商仲裁功能。以下为原理实现框图:详细的设计请参考我之前写的文章:直接点击前往

5、AD7606 UDP传输详细设计方案

AD7606 UDP传输详细设计方案如下:

用示波器产生一个正弦波作为输入源给到AD7606,AD7606数据采集支持并行和串行模式,在工程代码的顶层文件里做了整合,如下:

采集后的AD数据送DDR3缓存,这个数据缓存模块不仅可以缓存AD数据,还可以缓存图像数据,并做了4帧缓存模式,因为本设计主要介绍UDP的组包,所以数据缓存模块不做过多介绍,感兴趣的可以查看详细的源码。

UDP应用的设计思路

UDP本身只是一种通信协议,用verilog实现并不难,他的精髓在于应用,而UDP应用的要点在于数据的组包与拆包,就本设计而言,FPGA作为发送者,需要将AD7606采集的数据进行组包,拆包是上位机软件干的事儿。

注意!!!

这里的组包指的是在以太网帧格式的UDP有效数据段人为的组包,并非UDP协议里固定的帧头等信息的组包,这里的组包是为了两个节点之间的收发对应。。。

通信开始后,上位机会发送查询命令给FPGA,FPGA则将本地网卡的基本信息和AD7606的数据信息发送给上位机,上位机得到FPGA网卡的信息后会选择对应的拆包和现实程序,FPGA会按照自己定义的UDP数据包向上位机发送数据,这样一来,一个简单的UDP通信应用就组件完成了。。。

本设计组包协议如下:

获取FPGA网卡信息

询问命令(共 5 字节,由上位机通过以太网发送)

应答命令(共 27 字节,由开发板通过以太网发送)

代码层面表现如下:(eth_cmd.v)

获取数据

控制命令(由上位机发送数据请求)

每个 UDP 包都包含有 Header,在第一个字节,其格式如下:

UDP发送数据组包

注意!!!

注意!!!

注意!!!

这里是整个工程的重点,AD7606的数据就是以这个格式发送出去的:

代码层面表现如下:(mac_ctrl.v)

UDP发送流程

首先在空闲状态,上位机会通过以太网广播发送询问命令,因此在 IP 层接收时要加上判断是否是广播 UDP 数据,如果是,也接收数据,此段代码在 ip_rx.v 中,如下所示:

之后在 eth_cmd.v 文件中判断接收到的数据信息,是否是询问命令或控制命令,从而产生出

命令的应答请求信号 cmd_reply_req,或请求数据的信号 ad_data_req。

eth_cmd.v 模块顶层接口如下:

mac_ctrl.v 文件实现以太网的传输控制,在 IDLE 状态下等待一定时间,进入 CMD_WAIT 状态,判断是否有命令请求 cmd_reply_req 或数据请求 ad_data_req,之后进入 CHECK_ARP 状态,检查对

应的 IP 地址是否在缓存列表中,如果没有,将发送 ARP 请求,等待应答。之后根据命令请求或数据请求进入相应的数据发送状态,CMD_SEND 或 AD_SEND 状态。

mac_ctrl.v 模块顶层接口如下:

上位机设置的缓存空间为 1M 字节,请求数据间隔为 100ms,因此在设置采样深度时要考虑到这两点。在 eth_top.v 程序中设置为 32’h00008000,即 32K 字节,采样频率为 200KHz,ADC 采样端数据为两个字节长度,因此采样长度为采样字节除以 2,即 32’h00004000,计算需要82ms 可采集完成。移除了 UDP 发送数据的检验和。

代码层面表现如下:(eth_top.v)

6、vivado工程详解

工程介绍:

开发板:Xilinx Artix7开发板;

开发环境:vivado2019.1;

网络PHY:KSZ9031;

输入:AD7606;

输出:UDP-RJ45网口;

工程代码架构如下:

FPGA资源消耗和功耗预估如下:

7、上板调试验证并演示

上位机软件位置如下:

上位机未收到数据时如下:

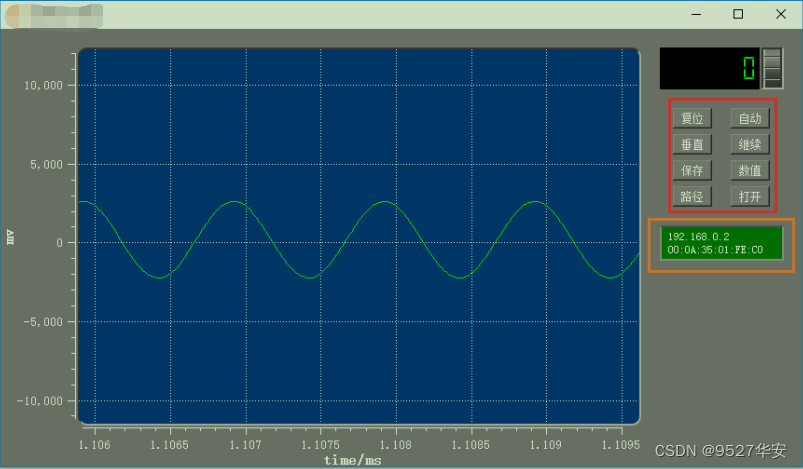

用示波器产生一个5V的正弦波接入AD7606转接板,上位机现实波形如下:

绿色框显示发送板卡的 MAC 和 IP 地址;

复位:点击复位可使波形显示到初始状态;

垂直:“垂直“与“水平”切换,点击此按钮可进行水平垂直方向缩放的切换,在垂直状态下,滚动鼠标滚轴可进行垂直方向的缩放,水平状态下,进行水平方向的缩放;

暂停:“暂停“与”继续“切换,点击暂停波形,可再点击“继续”显示波形;

保存:保存 ADC 数据为 TXT 文档,保存路径在“路径”按钮处设置,默认为软件所在路径;

数值:“数值”与“电压”切换,Y 方向坐标单位为原始值,即接收到的原始数据值,点击“电压”则显示电压值;

路径:选择保存路径;

打开:打开已保存的 TXT 波形文件;

8、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献28条内容

已为社区贡献28条内容

所有评论(0)