JESD204b接口使用实例

接触的第一个项目中涉及到JESD204b接口的问题。由于初次接触,并且对使用的AD/DA芯片不是很熟悉,所以遇到了一些问题。摸爬滚打后项目算是跑通了,将有关该接口的总结与心得记在这里。文章结合实例先后给出了JESD204b接口的介绍、参数、实际配置流程。JESD204是基于SERDES的串行接口标准,主要用于AD/DA芯片和逻辑器件之间的数据传输,最早版本的是JESD204a,现在是JESD204

文章目录

前言

接触的第一个项目中涉及到JESD204b接口的问题。由于初次接触,并且对使用的AD/DA芯片不是很熟悉,所以遇到了一些问题。摸爬滚打后项目算是跑通了,将有关该接口的总结与心得记在这里。文章结合实例先后给出了JESD204b接口的介绍、参数、实际配置流程。最后给出了我自己遇到的问题。

一、JESD204b接口介绍

JESD204是基于SERDES的串行接口标准,主要用于AD/DA芯片和逻辑器件之间的数据传输,最早版本的是JESD204a,现在是JESD204b,包括子类0,子类1和子类2。本设计中采JESD204b的子类1模式,最大传输速率可以达到12.5Gbps。

JESD204b的工作过程可以分为以下三个步骤:

首先是代码组同步。发送端和接收端之间有一个SYNC信号互连。接收端发出同步请求,拉低SYNC信号。当发送端检测到SYNC信号为低电平时,会发送一种K码。当接收端收到K码时,会拉高SYNC信号,从而完成代码组同步过程。

第二个过程为发送初始化多帧序列。当发送端检测到SYNC信号的变化时,会在下一个本地多帧边界时发送连续4个初始化多帧(多帧是由K个帧组成,字节数为K*F),此样本数据段不进行扰码和字节替换。这个过程的目的是对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据中的位置。

第三个阶段即为数据传输阶段。该阶段的数据需要进行字节替换,并且用户可以根据需求决定是否为数据添加扰码。

二、JESD204b参数

JESD204b接口可以通过配置不同的参数,来决定传输的链路数、线速率等指标。

1.参数描述

| 参数 | 含义 |

|---|---|

| M | 转换器个数 |

| N | 转换器分辨率 |

| N’ | 半字节位数 |

| F | 每一帧的字节数 |

| S | 每一帧的采样数 |

| K | 多帧情况下的帧数 |

| L | 通道数 |

| fc | 基带采样率 |

2.参数关系

其中,M为转换器个数,N为转换器分辨率,N’为半字数量乘以4,其中半字节长度为4位,则14位采样率的转换器,其半字节数应该为4,则N’取值为16。F为每一帧字节数,S为每一帧的采样数,L为接口采用的通道数,fc为基带采样率。coreclk为核时钟,lanerate为线速率。式中的10/8是因为数据传输过程要进行8B/10B的编码。

三、 实例

1.配置参数计算

本示例中,在数据发送部分,FPGA端的JESD204b接口为发射端,DA芯片端的JESD204b接口为接收端;在数据接收部分,AD芯片的JESD204b接口为发射端,FPGA端的JESD204b接口为接收端。

首先确定AD/DA芯片采用的JESD204b模式为模式4。

根据AD/DA芯片手册,得到模式4下的L_M_F参数为:4,4,2。

根据基带信号处理部分,得到基带采样率为500MHz.

根据以上参数及前述公式,可以计算得到线速率为10GHz,核时钟为250MHz.

2.IP核的配置

涉及到的IP核:JESD204 PHY,JESD204

JESD204 IP核需要具有完整的license,才能进行综合、布线、生成bit文件等。

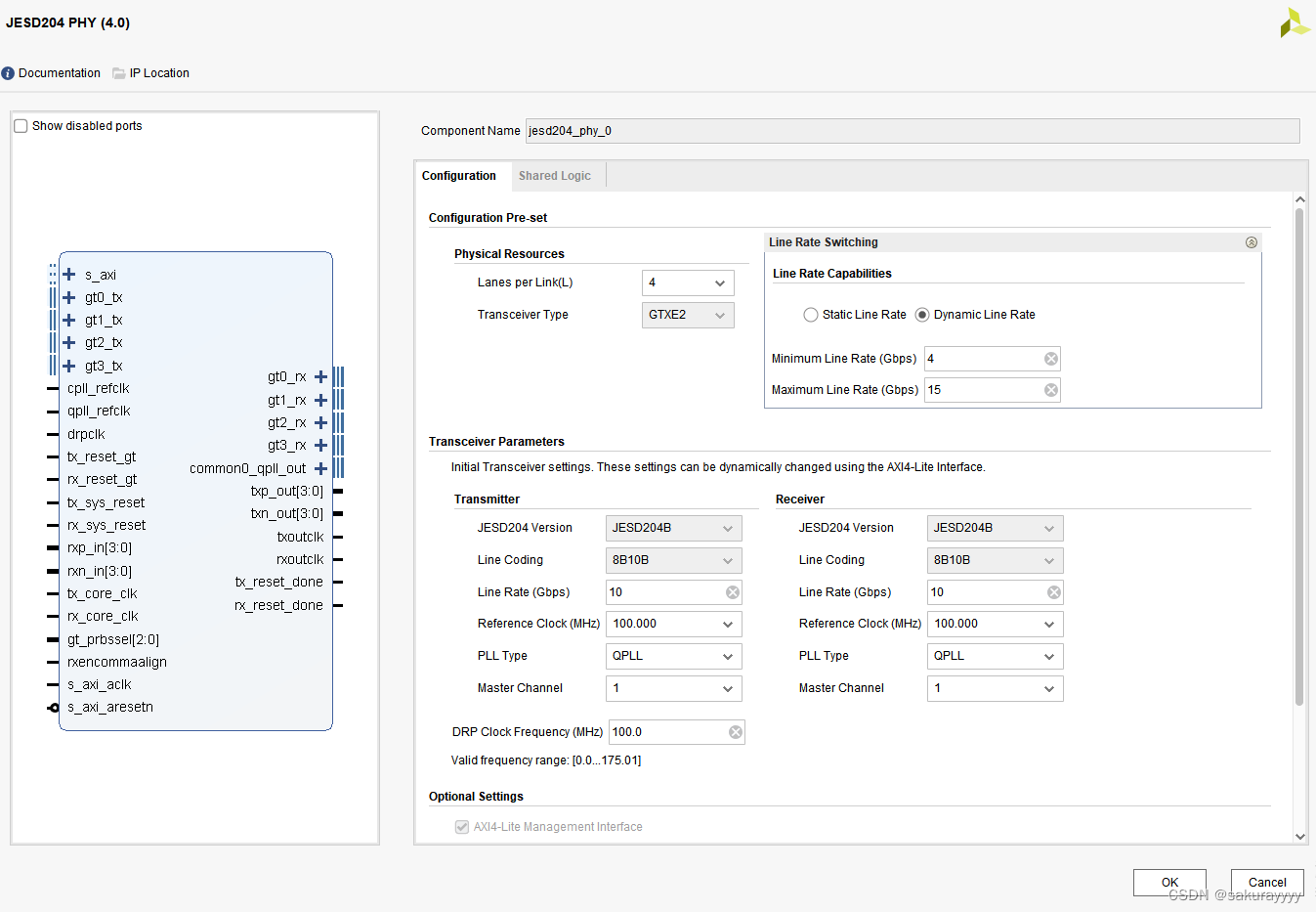

JESD204 PHY的配置:

lanes per link 即为通道数L,Line Rate为线速率。参考时钟按照实际时钟配置即可。

JESD204 的配置:

首先配置发射还是接收。lanes per link同上。

shared logic部分,选择include shared logic in example design则需要进行JESD204 PHY核的配置。本示例中采用该种模式。

3.常见问题:

3.1 参数确定问题

基带采样率要确定好。这个需要和基带信号处理部分一起考虑。由于当时基带部分还没有完成,只是想先把接口测试好,所以基带采样率的问题就没有考虑,只是随便给了个信号。

3.2芯片配置问题

如果确定FPGA这边的设置没有问题,那就有可能是AD/DA芯片的配置出现问题。芯片配置部分要好好阅读芯片手册。两边采用的模式要一致。

3.3 SYNC信号的抓取

FPGA和芯片完成同步的标志是SYNC信号的拉高。可以通过抓取SYNC信号检查两端是否完成同步。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)