IC设计版图和基本单元的理解

因此,场氧是覆盖。

IC设计版图的理解

本文是笔者根据经典教材专用集成电路第二章CMOS逻辑部分得出的一些理解,如有问题,请提出指教。

参考链接:

1.CMOS工艺流程详解说

2.中科大PPT

从三极管制造说起

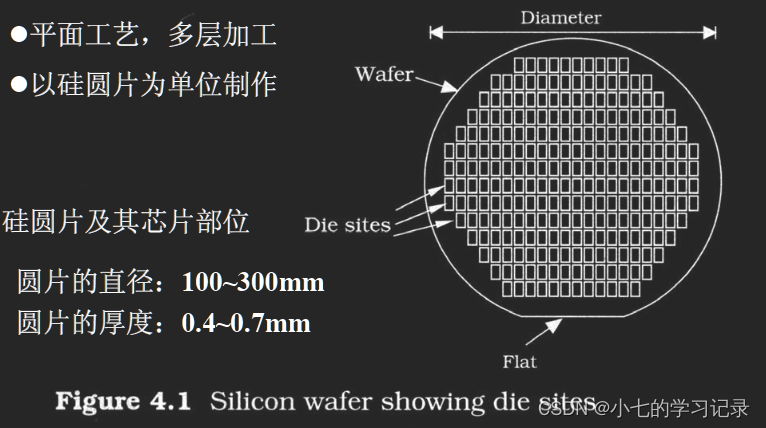

我们知道三极管(或者可以说半导体,二极管)是由大量硅作为基质材料,通过向其中掺杂不同的介质形成P型或N型二极管,而这个基底材料在最初始形态叫做晶圆。

晶圆

晶圆使用单晶硅作为材料,通常由制造厂向化学场采购获得。顾名思义,晶圆是单晶硅圆柱,如下图所示:

由于二氧化硅的掩蔽杂质特性——在集成电路制造中,如硼、磷、砷等常用杂质在SiO₂膜中的扩散要比在Si中慢得多,因此需要在高温炉中生长一个氧化层(二氧化硅),通过氧化层的屏蔽特性,选择性的向硅中掺杂介质才得到二极管。

甩胶

由于我们希望把我们想要制造的电路印刷到晶圆上,因此我们需要一个掩膜,使得其中空部分可以被印刷,而掩盖住的部分无法印刷,二氧化硅层就是第一掩膜层,而我们还需要掩膜选择性的保留二氧化硅,而光刻胶(耐蚀膜)起到的就是掩膜二氧化硅的作用。通常会有一个机器把光刻胶溶剂(此时是液态)滴在晶圆(氧化后)上,然后机器会拖着晶圆高速旋转,通过离心力使晶圆均匀涂在表面上,在烘烤使溶剂固化留下固体光刻胶。

那此时光刻胶是均匀覆盖,并没有掩膜的作用,好在光刻胶有一个特性:在被紫外线照射后会溶解(消失),那么我们只需要再做一个掩模版挡住我们想要留住光刻胶的部分就好了。

曝光与显影

这里有三个重要的概念:

光刻:图形由掩模转移到光刻胶上

刻蚀:图形由光刻胶转移到光刻胶下面的材料上(二氧化硅)

掩模:一块有铬图案的玻璃板

所谓的后端设计就是在设计掩膜的过程,通过掩膜对平行光的阻挡与透过使得光刻胶部分被融化(透光),部分不变(遮光)

之所以分成曝光与显影,相信玩过早期相机同学都知道,曝光后要隔一段时间(显影)才有图像。

刻蚀

那么现在我们的晶圆长成了这样:

从下到上依次是:单晶硅->二氧化硅->光刻胶(光刻后)

接下来才轮到我们制作真正的掩模版了(二氧化硅层),通常有干法或湿法(腐蚀),反正就是借助光刻胶的阻挡,选择性的去除二氧化硅(去除的二氧化硅是光刻胶没有阻挡的部分)

离子注入

那么现在我们的晶圆长成了这样:

接下来我们要掺杂的离子注入到单晶硅里面了,通常有一个机器加速离子,将他均匀射向晶圆,由于二氧化硅离子扩散慢,因此把离子阻挡下来了,而没有二氧化硅的部分被注入了离子,根据注入离子的不同形成了P阱或N阱(阱的意思是在衬底画出一片区域变成另一种材料,等下会讨论为啥要阱)。注意,此时注入的是阱部分,是下面二输入与门版图中的黄色和绿色的部分!!!不是深红色部分(这两部分在n/p-扩散注入形成)

这里还有一个衬底的概念,衬底通常指晶圆片本身(可被制作为P型或N型)。

衬底和阱的关系如下图所示

去胶 去氧化

现在我们的晶圆长成了这样:

接下来需要把光刻胶和二氧化硅全去掉(但是二氧化硅一会还会再回来)。

秃了,就剩单晶硅层了:

生长其他层

注意,之前我们还只是生成了大片的阱区(衬底区)(此时阱区和衬底区概念可以合并了),还不是我们真正实现三极管的区域,需要在阱上再扩散注入,才得到我们真正生成三极管的区域(下面二输入与门的版图的黄色和绿色部分)

此时引入两个概念:

场氧:是为了实现隔离,也就是防止出现寄生管

栅氧:是为了实现绝缘栅介质

场氧(FOX):

源区、漏区、沟道区合称MOS管的有源区,有源区之外的区域定义为场氧区(Fox)。有源区跟场氧区之和就是整个芯片表面因此,场氧是覆盖二输入与门的版图中除黄色绿色和红色带状以外的区域。起到隔离作用。

栅氧:

用作晶体管的栅绝缘层,主要起到绝缘作用

生长多晶硅

利用光刻胶再次刻蚀多晶硅

n/p-扩散注入

注入对应的离子,形成下面二输入与门中深红色的部分,同时为多晶硅附上导电介质(形成电压传导)

氧化与钨塞生成

氧化层负责隔离,钨塞负责导电,钨塞也可以接触到多晶硅的导电区

上图中,黑色的部分为钨塞

金属层

上层可用金属线把钨塞点按版图连接起来了!

从版图到原理图

参考网址:基本单元版图与电路图

这是一个二输入与门的版图:

其中深红色方块代表VIA过孔和有源区,黄色部分代表P阱,绿色部分代表N阱,红色部分代表浮栅,橘色边框部分代表输入/输出连接点,紫色部分代表连接线。

举例:源区/漏区->深红色方块,耗尽区->黄色/绿色区域,栅区->红色条状线

这是其对应的电路原理图

观察规则:每两个深红色方块和一个浮栅组成一个三极管,以下是对应关系:

从表达式到原理图

我们先不提从原理图到表达式,这个比较复杂

假设我们要构建一个CMOS的与门

Z=A·B

我们可以先画出其卡诺图:

从附记1中强弱逻辑我们可以看出:P驱动1的能力强,N驱动0的能力强

所以分别针对卡诺图中的0和1写出对应的表达式:

P: A·B

N:~A+~B(使用卡诺图化简,把0暂时看成1)

从附记2中推进反相符,由于需要P型需要推进反相门,N型需要推远反相门

P:A·B=~~(A·B)=~(~A+~B)

N:~A+~B=~~(~A+~B)=~(A·B)

可以同时提取非门,而形成上述电路图(P型天生具有反向作用)

从原理图到表达式

通过原理图我们可以分别写出P和N的表达式:

注意:PN之间不能简单用并连接,不是或逻辑,而是传输门逻辑(含高阻态)

再写出最小多项式:

最后在卡诺图中,P对应部分填入1,N对应部分填入0,再写出表达式即Z=A·B

附记:

CMOS中的强弱逻辑

考虑一个n沟道晶体管:

强逻辑

假设漏端D初始逻辑为1(此时默认源端直连VSS,所以电压不变),假设漏断连接另一个逻辑单元

这里把另一个逻辑单元抽象为一个电容的原因:驱动肯定是接到了另一个逻辑单元的浮栅端,而浮栅相对于沟道是电容,不会向外导电!!!

由于是N型CMOS,所以VG比VS大1的情况下,沟道强导通,导电沟道很宽,使得D端电压下降到跟S一样大使得VGD=VGS=VDD=逻辑1,但因为VDS=0,所以没有电流流过。

弱逻辑

此时把1加到漏极必须是漏极,,因为电子必须流向逻辑1(源端加1就不导通了)。

假设源端初始为0,在晶体管导通时VGS电压不断下降(VS上升逼近VG【VDD】)

但是VS永远到达不了VDD,因为当VGS到达Vtn(截止电压)晶体管几乎截至,源端电压不会上升。

源端电压慢慢升到VDD-Vtn,晶体管接近截止,沟道很窄几乎没有,所以为弱1

结论:N型强0弱1,P型强1弱0

因此上述原理图中接入VDD喜欢用P型,接入VSS喜欢用N型

推进反向符

由于P型晶体管天生具有非逻辑(不完全的,接近传输门,因为有高阻态)

所以在使用时可以将非逻辑推入输入端:

举例:

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)