Verilog编译预处理

编译预处理是Verilog HDL编译系统的一个组成部分。Verilog HDL编译系统通常先对这些特殊的命令进行预处理,然后将预处理的结果和源程序一起在进行通常的编译处理。为了和一般的语句相区别,这些预处理命令以符号 ` 开头这些预处理命令的有效作用范围为定义命令之后到本文件结束或到其它命令定义替代该命令之处。一般形式// 宏定义`define 宏名 宏内容// 使用宏`宏名宏名的有效范围为定义

一、简介

编译预处理是Verilog HDL编译系统的一个组成部分。

Verilog HDL编译系统通常先对这些特殊的命令进行预处理,然后将预处理的结果和源程序一起在进行通常的编译处理。

为了和一般的语句相区别,这些预处理命令以符号 ` 开头

这些预处理命令的有效作用范围为定义命令之后到本文件结束或到其它命令定义替代该命令之处。

宏定义与parameter的区别

二、宏定义`define

一般形式

// 宏定义

`define 宏名 宏内容

// 使用宏

`宏名

宏名的有效范围为定义命令之后到原文件结束。

宏定义是用宏名代替一个字符串,也就是作简单的置换,不作语法检查,预处理时照样代入,不管含义是否正确。只有在编译已被宏展开后的源程序时才报错。

在进行宏定义时,可以引用已经定义的宏名,进行层层替换。

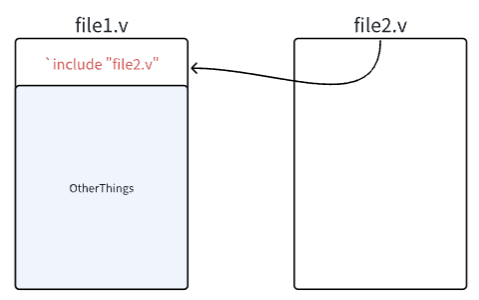

三、文件包含`include

文件包含处理是一个源文件可以将另一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。

Verilog语言提供了include命令用来实现文件包含的操作。

`include "文件名"

预处理时,会将file2.v中的全部内容复制插入到include “file1.v” 命令出现的地方。

在后面的编译中,会将包含以后的file1.v作为一个源文件单位进行编译。

文件包含可以将一些常用的宏定义命令或者任务task组成一个文件,然后用include命令将这些宏定义包含到源文件中。

此外一个源文件可能经常要用到另外几个源文件中的模块,可以使用include命令将所需模块源文件包含进来。

文件包含的说明:

- 一个include命令只能指定一个被包含的文件,如果要包含n个文件,需要用n个include

- include命令可以出现在Verilog源程序的任何地方,被包含文件名可以是相对路径,也可以是绝对路径。

- 如果文件1包含文件2,而文件2要用到文件3的内容,则可以在文件1中用两个include命令分别包含文件2和文件3,并且文件3应出现在文件2之前。(此时文件2中可以不用包含文件3)

- 在一个被包含文件中又可以包含另一个文件,即文件包含是可以嵌套的。

四、时间尺度`timescale

timescale命令用来说明跟在该命令后的模块的时间单位和时间精度。

使用timescale命令可以在同一个设计里包含采用不同时间单位的模块。

timescale命令格式:

`timescale 时间单位/时间精度

时间单位参数用来定义模块中仿真时间和延迟时间的基准单位,时间精度参数用来声明该模块的仿真时间的精确程度,即决定模块中的延迟时间可以带几位小数。

如果在同一个程序中,存在多个timescale命令,则用最小的时间精度值来决定仿真的时间单位。

时间精度至少要和时间单位一样精确,时间精度不能大于时间单位值。

用于说明时间单位和时间精度值的数字必须是整数,其有效数字为1、10、100,单位为: s、ms、us、ns、ps、fs。

可以使用系统任务$printtimescale来输出显示一个模块的时间单位和时间精度。

可以使用系统函数$time和realtime及%t格式声明来输出显示EDA工具记录的时间信息。

五、条件编译`ifdef

一般情况下,Verilog源程序的每一行都参与编译,但是有时希望对其中的一部分内容只有在满足条件才进行编译,就需要使用条件编译。

条件编译形式

///

`ifdef 宏名

// xxx

`else

// xxx

`endif

///

`ifdef 宏名

// xxx

`endif

///

`ifdef 宏名

// xxx

`elsif 宏名

// xxx

`else

// xxx

`endif

被忽略的不进行编译的部分也要符合Verilog程序的语法规则。

通常在Verilog中使用条件编译的情况有以下几种:

- 选择一个模块的不同代表部分。

- 选择不同的时序或者结构信息。

- 对不同的EDA工具,选择不同的激励。

ifdef和generate的对比

参考

- https://zhuanlan.zhihu.com/p/72091202

- https://zhuanlan.zhihu.com/p/359329515

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)