AD高速板设计--HDMI(笔记)

HDMI的布线要求:差分线对内误差为5以内,所有的差分线误差在10以内:进行阻抗匹配需要调整线宽,间距和板层。四对差分线,控制阻抗为100欧姆;四对单端信号线,控制阻抗为50欧姆。\]HDMI识别过程:HDMI的IIC采用的是HDMI的IIC采用的是,板载的IIC通常采用的是3.3V或者1.8V的电平标准,我们在使用的过程中,应当进行电平转换。,此处我们采用。

HDMI的布线要求:

差分线对内误差为5以内,所有的差分线误差在10以内:

进行阻抗匹配需要调整线宽,间距和板层。

四对差分线,控制阻抗为100欧姆;四对单端信号线,控制阻抗为50欧姆。

\]

\]

HDMI识别过程:

HDMI的IIC采用的是5V电平标准。

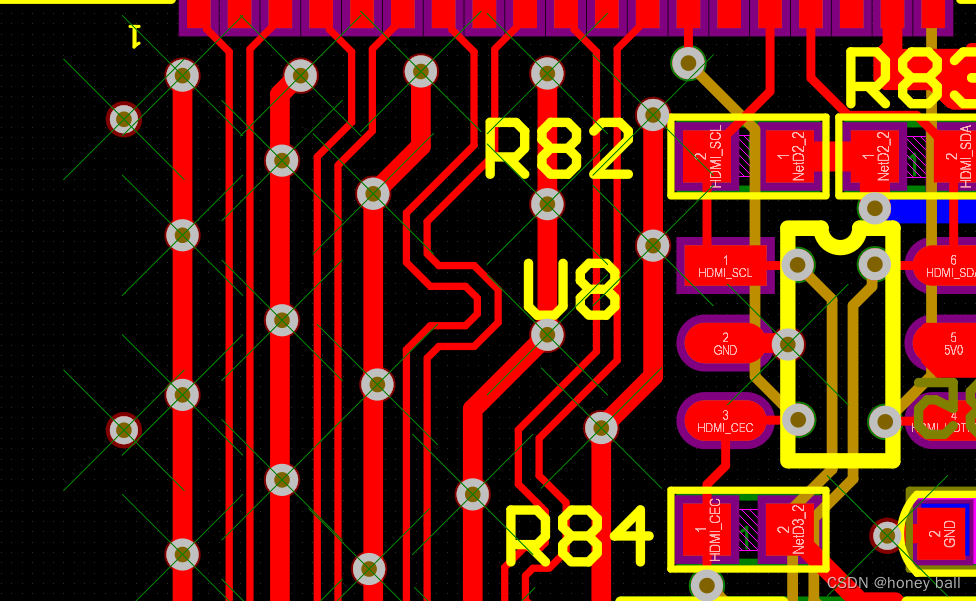

HDMI的IIC采用的是5V电平标准,板载的IIC通常采用的是3.3V或者1.8V的电平标准,我们在使用的过程中,应当进行电平转换。,此处我们采用MOS管搭建双向转换电路,如下图其目的为将RK3399板载的1.8V电平标准转换为5V的:

5V在这里做了个Y线,实际上是两个I2C7_SCL_HDMI ,I2C7_SDA_HDMI从主控RK3399引出之后分别做了电平转换,之后得出DDC_SCL,DDC_SDA经过ESD防护之后接到HDMI 接口上。

在这里先回顾一下MOS的知识,便于后续分析:

NMOS(MOS中两个二极管同时由S极发出到D极的为NMOS;MOS中两个二极管从G极和D极共同流向S极的为PMOS)

negative ----NMOS(二极管逆着G极,消极的) ; positive-----PMOS;(二极管顺着G极,积极地)

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

简易版的IIC的电平转换电路:

Q1为NMOS(MOS中两个二极管同时由S极发出到D极的为NMOS;MOS中两个二极管从G极和D极共同流向S极的为PMOS),Q1中左侧为S极,右侧为D极,上侧为G极。

A=0时,Vgs=3.3V,此时MOS管导通,B=0;

A=1时,Vgs=0V,此时MOS管截至,B=1;

B=0时,A=0;

B=1时,MOS管截止,A段上拉,A=1;

为什么PCB中电源旁边都喜欢放一个电阻:

仅这几个引脚需要进行电平升高,VCC_1V8需要根据主控的IIC电平标准来弄,也有可能不是1.8V是3.3V。其他的差分数据线直接跟接口连接,中间为防止静电加上ESD防护器件即可。

全志H616中直接采取了上拉措施,没有进行电平转换的那一步,哪一个更好呢?直接用5V上拉是不是不太妥当呢,我觉得这样到HDMI的5V没有1.8--5v电平转换电路的5V稳定标准。

来自全志的官方设计指导文档这里给了解释,如下:(设计板子时候多看官方文档,每一部分都有注意事项)

破案!

GPT解释如下:

包地处理:

快捷键RS测量单根导线的长度:

快捷键RP测量两根导线之间的距离:

这里也可以查看每个线的长度:

绕等长的时候从信号的源端绕,不能从信号的末端绕。

手工版本拐线加长:没有蛇形走线优雅,但做的很快

RS测量出来的导线长度是Routed Length。

立创EDA走圆弧角线的方法:

一种挺漂亮的按键:

器件:TSA017A2540A03 封装:SW-SMD_4P-L4.2-W3.4-P2.15-LS5.2

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献21条内容

已为社区贡献21条内容

所有评论(0)