一文讲清楚PCIE中的alignment和lock

Symbol lock更多的是针对8b/10b编码的场景来说的,对于128b/130b编码,完成了block alignment,就可以识别出ordered set或者block了,不再需要symbol lock。无论是block alignment,还是symbol lock,基础是需要是先识别出对端发送过来的码流,从对端发送的信号中识别并恢复出各个bit。这个恢复出各个bit的过程就是bit

一文讲清楚PCIE中的block alignment,symbol lock和bit lock。

1. Block alignment

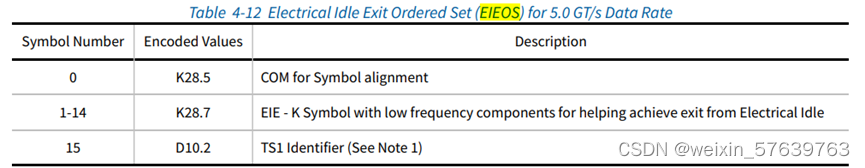

首先介绍三个概念:block sync header、block和Electrical Idle Exit Ordered Set(EIEOS)。

在PCIE中,8GT/s及以上的速率,采用的是128b/130b编码。128-bit是想要传输的payload,实际会传输130-bit,多出来的2-bit就是sync header。

Block有两种,通过Sync header区分:

- 10b:表示data block,data block就是10b的sync header加一系列叫做“data stream”的symbols,data stream包括了framing tokens,TLPs和DLLPs等。data block主要用于传输数据和信用交互。

- 01b:表示Ordered Set block,由01b的sync header加上一个ordered set组成,ordered set有TS1, TS2, EIOS, EIEOS, FTS和SKP等,ordered set主要用于链路训练(也有其它作用,如SKP OS用于频偏补偿)。

00b和11b是非法的sync header,对于各种framing tokens和各种ordered sets的具体含义和作用,这里不展开,后面有机会再单独用一篇文章细说。

如下图所示,一般情况下,link中所有的lane都要同时传输相同的sync header。

EIEOS就是ordered set中的一种,这是一个低频的pattern,用来保证receiver可以检测到对端退出electrical idle的状态,在128b/130b编码时,也用来做block alignment。在32GT/s及以上时,一个Electrical Idle Exit Ordered Set Sequence(EIEOSQ)由两个EIEOS组成。在5GT/s,8GT/s及16GT/s时,一个EIEOSQ只有一个EIEOS。

不同速率下的EIEOS具体如下:

简单来说,就是通过连续的0和1来达到实际上的降频效果,所以说,EIEOS是一种低频的pattern。

所谓block alignment,可以简单理解为receiver用接收到的Electrical Idle Exit Ordered Set去锁定block sync header的过程,或者说是一种锁定住了block sync header的状态。Block alignment有3个phases:

- Unaligned phase:receiver进入electrical idle之后,就会进入状态,然后开始等待EIEOS,detect到EIEOS并且align后,进入aligned phase;

- Aligned phase:receiver继续根据收到的EIEOS进行align(如果需要的话),如果收到了SDS ordered set,receiver会进入lcoked phase;如果检测到undefined的sync header(00b或11b),receiver可以回到unaligned phase;

- Locked phase:在这个phase,receiver不能再调整alignment,如果检测到undefined的sync header(00b或11b),receiver必须回到unaligned phase。

2. Symbol lock

Symbol lock是receiver从一连串码流中识别出某个特殊symbol,从而识别出ordered set的过程,这个symbol一般是ordered sets中的第一个COM symbol。

在链路训练过程中,receiver在polling.active,recoverylock,以及L0s跳转到L0时(transmitter会发送连续的FTS)完成symbol lock。

Symbol lock更多的是针对8b/10b编码的场景来说的,对于128b/130b编码,完成了block alignment,就可以识别出ordered set或者block了,不再需要symbol lock。

在8b/10b编码中,COM是K28.5:

3. Bit lock

无论是block alignment,还是symbol lock,基础是需要是先识别出对端发送过来的码流,从对端发送的信号中识别并恢复出各个bit。这个恢复出各个bit的过程就是bit lock。

Bit lock依赖于PCIE中底层的Serdes电路完成,Serdes电路中有一个专门的clock & data recovery模块来实现从收到的信号中恢复出时钟和bit流。CDR是一个非常复杂的技术,值得专门写一篇讨论,这里不做展开。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)