VHDL语言基础-基本语句

VHDL语言基础-基本语句;VHDL语言与高级程序语言最大的不同就是VHDL语言是并发执行的,但是VHDL的基本语句包括顺序语句和并行语句。

目录

VHDL基本语句:

VHDL语言与高级程序语言最大的不同就是VHDL语言是并发执行的,但是VHDL的基本语句包括顺序语句和并行语句。

顺序语句不能直接用在结构体中,需要用process 进行“封装”

VHDL中,不区分大小写,使用“--”表示注释

并行语句:

并行执行,其执行方式与书写顺序无关

假设信号原始值为 假设信号原始值为a=1;b=1;对于以下两种书写格式,执行结果如下:

并行语句常包括以下七种:

赋值语句、条件赋值语句、选择信号赋值语句、进程语句 、元件例化语句 、生成语句 、子程序调用语句

赋值语句:

将一个值或一个表达式的运算结果传递给某一数据对象。

使用格式:

注意:信号赋值符号为“<=”;变量和常量的赋值符号为 “:= ”

条件赋值语句:

根据执行条件,将一个值或表达式的的运算结果赋给赋值目标

使用格式:

注意:每一个子句结尾没有任何标点,只有最后一句有分号

选择信号赋值语句:

根据选择值的匹配,将一个值或表达式的的运算结果赋给赋值目标

使用格式:

注意:选择信号赋值语句的每一个子句结尾是逗号,最后一句是分号

进程语句:

本身是一个并行语句,内部是由顺序语句组成

使用格式:

注意:进程启动有两种方式:敏感列表和wait语句

Example:D触发器:

在此例中,PROCESS由敏感参数表中的reset、clk或d当敏感信发生变化时启动进程

在此例中,PROCESS由wait on语句启动,当等待到in1,in2信号发生变化时,进程再次执行。

进程语句的特点:

- 进程本身是并行语句,一个结构体可以包含多个进程

- 已列出敏感量的进程不能使用wait语句

- 进程语句的启动只能是信号的变化

- 当一个进程执行结束后,先挂起来,一直到有新的启动信号变化为止

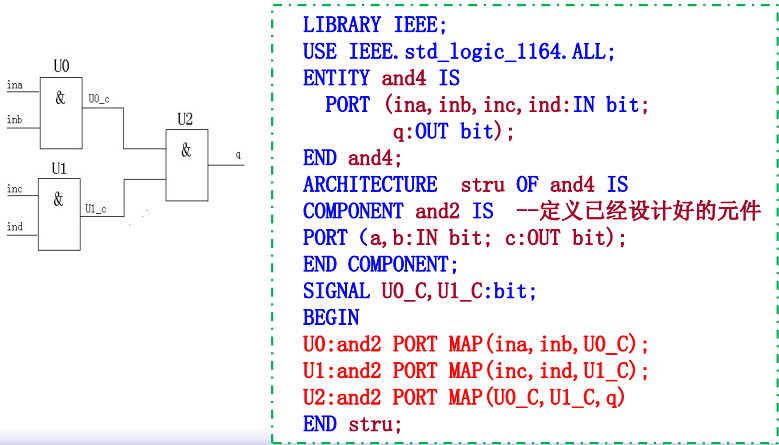

元件例化语句:

将预先设计好的元件与当前设计实体中的指定端口相连接

使用格式:

注意:元件例化语句由两部分组成,前一部分是把一个现成的设计实体定义为一个元件,第二部分则是此元件与当前设计实体中的连接说明。

元件例化语句——Example:4输入与门

生成语句:

根据某些条件,复制 组完全相同的并行元件或设计单元电路结构

使用格式:

子程序调用语句:

调用其它程序,在执行完程序后返回需要的数据

使用格式:

注意 子程序的调用语句包括了过程调用语句和函数调用语句

顺序语句:

IF语句:

IF语句是一种流程控制语句,判断条件有先后次序 ,而且允许条件涵盖不完整

使用格式:

IF语句——Example:

IF语句与并行语句中的when…else条件赋值语句具有类似功能,可互换

CASE语句:

CASE语句与IF语句类似,也是一种流程控制语句

使用格式:

注意:

- CASE语句的选择值必须在表达式的取值范围内

- CASE语句的所有选择条件具有相同的优先权,不能有相 同选择值的条件句出现。

- 未能完全覆盖表达式的取值,则最末的选择值必须用 “OTHERS”

- 不想执行任何操作,可用保留字“NULL”描述

CASE语句——Example:

注意:CASE语句与并行语句中的WHEN …SELECT语句具有类似的功能,可互换 。

LOOP语句:

重复执行语句若干次或指导满足退出循环的条件为止

使用格式:

注意:与高级程序语言不同,里面的循环变量是不用定义说明的。

EXIT语句和NEXT语句:

- EXIT语句和NEXT语句都是LOOP语句的内部循环控制语句

- 执行EXIT 后,跳到循环体结束处跳到循环体结束处,立即退出循环

- 执行NEXT语句后,跳到循环体开始处,有条件或无条件终止当前循环迭代并开始下一循环

其它顺序语句:

等待语句WAIT:

返回语句RETURN:

空操作语句NULL:

属性描述语句:

VHDL中具有属性的项目包括 中具有属性的项目包括:类型 、子类型 、过程 、函数、信号、变量、常量、实体、结构体、配置、程序包、元件和语句标号等,属性就是这些项目的特性。

常用综合器支持的属性有:LEFT 、RIGHT 、HIGH 、LOW 、RANGE 、REVERSE_RANGE 、LENGTH 、EVENT 、STABLE 。

1.信号类属性:

EVENT表示信号发生率动作,STABLE表示无事件发生

2.数据区间类属性:

对属性项目取值区间进行测试,返回内容是一个区间如RANGE 和REVERSE RANGE

3.数值类属性:

·LEFT 、`RIGHT 、`HIGH 及`LOW这些属性函数主要用于对属性测试目标的数值特性进行测试

4.数组属性:

·LENGTH这个函数用于对数组宽度或元素个数进行测定

5.用户自定义属性:

属性与属性值的定义格式如下:

ATTRIBUTE 属性名:数据类型;

ATTRIBUTE 属性名 OF 对象名:对象类型 IS 值

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)