MOSFET正向导通,阻断,阈值电压研究

主要为MOSFET仿真其正向导通,正向阻断以及阈值电压相关特性曲线,分析其曲线的原因

一 设计要求:

- N-为均匀掺杂、其他均为离子注入所形成的高斯掺杂;

- P的宽度为10、结深6um;

- 氧化层oxide厚度为0.1um,宽度为10um;

- 氧化层左侧空白需要定义为材料air;

- 所有电极都定义为无厚度;

- 所有的高斯掺杂峰值点均在表面;

- 器件整体宽度为20um;

- 得到正向输出特性曲线、正向阻断电压曲线和阈值电压特性曲线;

- 正向阻断电压曲线为G-S短路;

- 正向输出特性曲线的门极电压为0-20V之间自己取值且取值至少五个点;

- ratio.lat=0.6;

- 顶部N+的结深为3um,宽度为2-5um,底部N+的结深2-5um;

- 阈值电压需要把Drain和Gate短接;

- 先定义N-均匀掺杂,再定义P高斯掺杂,再定义顶部N+高斯掺杂,在定义底部N+高斯掺杂;

- 器件阻断电压设计为600V,N-掺杂和厚度自己定义,满足以下表格中的要求即可;

| 区域 | 取值范围 |

| P 基区 | 0.5e17 – 5e17 |

| 氧化层 | 0.05 - 0.5(厚度) |

| Ratio.lat | 0.2-0.8 |

二 设计思路:

仿真MOSFET器件正向阻断特性和其他类似,主要由N-区做为最主要的耐压层,当超过器件最大阻断电压后器件电流呈直线上升、仿真MOSFET正向导通为给栅极施压超过阈值电压的电压,使得P区靠近氧化层出现反型层,使得器件导通、阈值电压仿真主要为栅极慢慢施加电压,观察器件何时导通,导通那点的电压为器件的阈值电压。

首先设定N-漂移区掺杂浓度为5e13,通过公式可得:

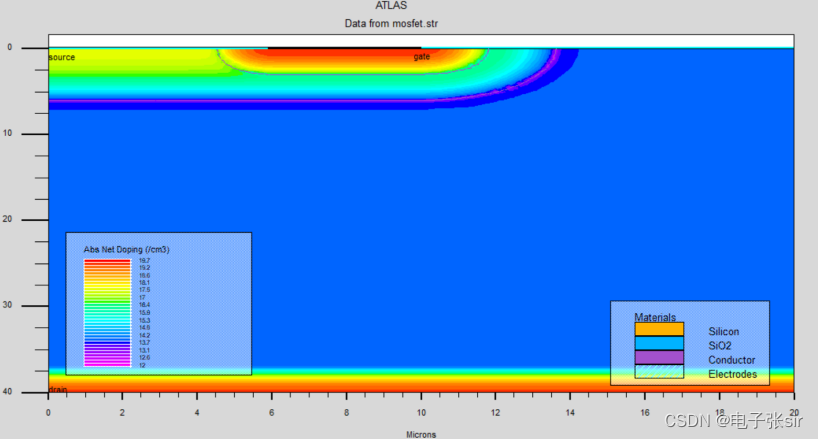

三 通过公式计算设定N-区长度为31um,p基区厚度为6um,氧化层厚度为0.1um,N+厚度为3um,整体厚度为40.1um,器件整体宽度设为20um,电极G宽度设为靠右10um,电极S设为宽度为6um,N-区掺杂为均匀掺杂5e13、底部和顶部N+基区掺杂为5e19、P掺杂为5e17,为可得整体结构如图4.1所示。

三 仿真结果:

通过设计好MOSFET的结构进行仿真,可以看到其主要结构和网格分布见图6.1所示,其中PN结在x=4.5、x=11.6和x=13.5各有一个。

图6.1 MOSFET结构仿真图

正向阻断特性曲线

图6.2 MOSFET正向阻断特性曲线

图6.2为MOSFET正向阻断特性曲线图、该曲线由GS短接,相对于D提供高电压获得、通过观察曲线可以得到曲线在550 v电压左右开始被击穿,曲线刚开始为较为缓慢的曲线当达到阻断临界电压曲线突变近似为垂线、可知MOSFET当DS施加电压时,空间电荷区主要在N-区扩展,N-区作为最主要的耐压层,当DS电压不断加大,由于N-区宽度为31um,当电压达到600v左右,主要发生为雪崩倍增效应,通过PN结空间电荷区电子和空穴漂移运动被加速,其动能增大,高能量,高速度的载流子不断与晶体原子碰撞,使共价键中电子激发的自由电子空穴对,新产生载流子在强电场作用下又被加速,重新获得能量,产生新的碰撞电离,导致载流子迅速成倍增加,从而使得器件被击穿出现大电流出现。

正向导通特性曲线

图6.3 MOSFET正向导通特性曲线

图6.3为MOSFET正向导通特性曲线图、该仿真曲线给基极施加一个超过阈值电压的电压,使得MOS出现反型层(沟道),通过给D施加正向电压而得到、通过改变阈值电压的大小从而得到5条曲线、分析最下面一条曲线,首先为线性上升区,然后变为缓变上升区最后到水平稳定区、这是由于当Vds小于某一值时,沟道不发生改变,可以将沟道看成是一个电阻,满足伏安特性于是为线性增大,当Vds逐渐变大后,使得漏极电流上升,沟道会逐渐夹断,于是会出现电流呈一个弧线上升,当Vds不断增大,沟道会夹断,使得器件进入饱和区,器件电流饱和,漏电流不会随着漏极电压上升而上升,于是在曲线中表现为一条水平直线,而施加不同的阈值电压会改变沟道的性质,从而导致不同的饱和电流。

阈值电压特性曲线

图6.4 MOSFET阈值电压特性曲线

图6.4为测试MOSFET阈值电压特性曲线图、该仿真曲线通过给G-D短接并且给S从0开始缓慢施加电压而得到、通过观察阈值电压特性曲线可以得到阈值电压为1.8v在未达到阈值电压前漏电流Id为0,当达到阈值电压后开始出现漏电流,并且呈一定速率上升,分析该曲线原因:可以知道MOSFET在上端部分存在MOS结构,p区中多子为空穴,少子为电子,并且沟道由电子构成,通过给D施加电压,其MOS结构会传递一定的电压到达p区的上表面,由于正极电压吸引电子聚集,Vd越则吸引的电子越多,当Vd达到阈值电压(即吸引的电子可以构成沟道使得器件导通)时,器件开始出现漏电流,其中p区多子为空穴但是导电沟道为电子构成,于是这个沟道区域也称反型层。

四 源代码

go atlas

mesh

x.m l=0 spacing=0.3

x.m l=3.5 spacing=0.2

x.m l=4.5 spacing=0.05

x.m l=5 spacing=0.1

x.m l=10 spacing=0.4

x.m l=11 spacing=0.2

x.m l=11.6 spacing=0.05

x.m l=12.5 spacing=0.15

x.m l=13.5 spacing=0.05

x.m l=14.5 spacing=0.2

x.m l=16 spacing=0.3

x.m l=20 spacing=1

y.m l=-0.3 spacing=0.02

y.m l=0.0 spacing=0.02

y.m l=1.5 spacing=0.5

y.m l=3 spacing=0.05

y.m l=4.5 spacing=0.5

y.m l=6 spacing=0.05

y.m l=10 spacing=2

y.m l=35.5 spacing=2

y.m l=36.5 spacing=0.5

y.m l=37 spacing=0.2

y.m l=38 spacing=0.5

y.m l=40 spacing=1

region num=1 silicon y.min=0 y.max=40

region num=2 oxide y.min=-0.3 y.max=0

electrode num=1 name=source x.min=0 x.max=6 y.min=0 y.max=0

electrode num=2 name=gate x.min=10 x.max=20 y.min=-0.3 y.max=-0.3

electrode num=3 name=drain bottom

doping reg=1 uniform n.type conc=5e13

doping reg=1 gauss p.type conc=5e17 ratio.lateral=0.6 x.min=0 x.max=10 peak=0 junct=6

doping reg=1 gauss n.type conc=5e19 ratio.lateral=0.6 x.min=6 x.max=10 peak=0 junct=3

doping reg=1 gauss n.type conc=5e19 ratio.lateral=0.6 peak=40 junct=37

save outfile=mosfet.str

tonyplot mosfet.str

models cvt srh print

impact selb

method newton trap

contact name=gate common=source

solve init

log outfile=mosfet.log

solve vdrain =0.001

solve vdrain =0.05

solve vdrain =0.2

solve name=drain vdrain=1 vstep=0.5 vfinal=10

solve name=drain vdrain=10 vstep=2 vfinal=50

solve name=drain vdrain=50 vstep=10 vfinal=650 compl=2.e-10 e.comp=3

tonyplot mosfet.log

quit更多关于阈值电压在实验报告中体现......

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)