数字电路 || 组合逻辑电路

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

组合逻辑电路

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

一、 组合电路的分析

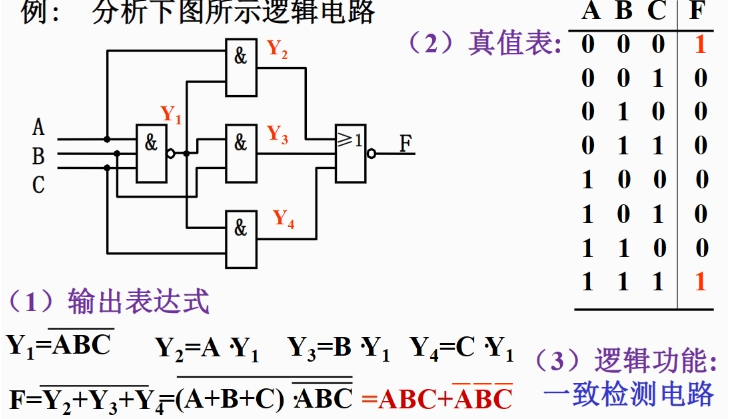

这里有一个思维训练题,为什么是一致检测电路呢?只有当A B C同时为1或同时为0时,最终结果才是1。

二、 组合电路的设计

首先我们回顾一下逻辑门电路:

然后做例题:

逻辑一致电路 / 逻辑不一致电路

三、 竞争-冒险现象

由于门电路延迟时间的关系,可能会使逻辑电路产生错误输出。这种现象称为竞争冒险。

竞争:在一个组合电路当中,当某一个变量经过两条以上的路径到达输出端的时候,由于每条路径上的延迟时间的不同,到达终点的时间就会有先有后,这一现象称作竞争。

冒险:逻辑门因输入端的由于竞争存在时间差,这个时间差会导致电路的输出产生与预期之外的窄的脉冲,这种输出产生不应有的尖峰干扰脉冲(又称过渡干扰脉冲)的现象叫做冒险。

- 冒险是由竞争造成的,而竞争是因为电路中的时延不同

分类

-

静态

(1) 功能冒险,是指由于电路中两个或者以上的信号发生变化时,由于电路和器件本身的特性导致的到达时间差而产生的冒险。功能冒险较之于逻辑冒险更难处理。

(2) 逻辑冒险,是指电路中只有一个信号发生变化却导致了输出产生冒险的现象。顾名思义,这是由于电路的逻辑设计的不合理导致。

-

动态

动态冒险是指当输入有变化时,输出应有变化,但输出在变化的过程中出现短暂的错误。

检查竞争冒险的常用方法:

1.逻辑表达式化简法

如果输出端门电路的两个输入信号A和A’是输入变量A经过两个不同的传输途径而来,则当输入变量发生变化时,输出端就可能产生尖峰脉冲。

故对于输出端的逻辑函数在一定条件下能化简成:

Y=A+A’ , 存在 “0” 型竞争;

Y=AA’ ,存在 “1” 型竞争;

的情况下,则判定一定有竞争冒险现象。

例:对于逻辑函数Y=AB+A’C

当B=C=1时,Y=A+A’,故此函数存在竞争冒险。

2.卡洛图法

即如果一个逻辑函数的表达式的卡洛图中所画圈没有重叠并且相切,则判定有竞争冒险。(本质上还是利用上面的方法,只是比较直观形象的判断)

对于以下卡洛图,左图存在竞争冒险,而由图不存在竞争冒险。

消除竞争冒险的方法:

1.增加冗余项,消除逻辑冒险。(卡洛图)

1)存在竞争的情况下,增加冗余项,实现输出消除毛刺。

例:逻辑表达式如下:Y = A’BC + AB

当B = C = 1时, 电路存在“0”型竞争。增加项:冗余项 B&C

更变后:Y = A’BC + AB + BC (利用消去冗余项公式)

2)还有卡诺图法,在两个相切的圆之间,相切接触的地方增加一个连接圆。

2)还有卡诺图法,在两个相切的圆之间,相切接触的地方增加一个连接圆。

对于上面的卡洛图,在相切的位置增加冗余项 B’C,故函数表达式Y=A’B’+AC+B’C

ps 还有一些其他的暂时看不懂就没加

四、编码器

优先编码器

普通编码器每次只能输入一个信号。而优先编码器可以同时输入几个信号,但在设计时已经将各输入信号的优先顺序排好。当几个信号同时输入时,优先权最高的信号优先编码

划重点:编码没有信号时,使能输出端ES有信号。

划重点:GS为扩展输出端,有编码信号输入时表现为有信号

问:将多片8线-3线优先编码器74148扩展为多线编码器的一般方法是什么?

答:设n个芯片相连,最高位芯片EI非作为编码器使能输入端,其他位芯片EI非和上一位EO非相连,GS非、A1、A2、A3为各芯片相与,其他An、An-1、…A4自最高位芯片开始依次以GS非作为输出

例题:【没搞懂😔】

注意,这里左边是低位芯片,右边是高位芯片。

五、译码器

以下内容需要重点研究:

尝试着解释一下,因为每个器件都只有两个输入端,于是我们固定让输入端为

I

0

I_0

I0和

I

1

I_1

I1,也就是最低的两位,高位通过使能端控制。

74138译码器

注意:G1,G2A和G2B是控制端,相当于译码器的开关。只有控制端都有效时,译码器打开,才可以进行译码,否则不能译码。结合高电平和低电平有效,只有G1是高电平有效,而G2A和G2B是低电平有效,也就是说,只有当G1为高电平,G2A,G2B都为低电平的时候,译码器才能正常工作,其他情况均不能。

一道易错题:

六、数据分配器

数据传输过程中,有时需要将数据分配到不同的数据通道上,能够完成这种功能的电路称为数据分配器,亦称多路分配器、多路调节器,简称DEMUX,其电路为单输入、多输出形式。其原理框图如图1所示。(所以数据分配器是一路输入,一路输出)

数据分配器和译码器的联系与区别

- 数据分配器和译码器有着相同的基本电路结构形式——由与非门组成的阵列;

- 在数据分配器中,D是数据输入端,A1A0是选择信号控制端;在二进制译码器中,与D相应的是选通控制端,A1A0是译码输入端;

带有使能输入端的二进制译码器通常即可用作数据分配器,n线- 2 n 2^n 2n线译码器即为1路- 2 n 2^n 2n路数据分配器。

数据分配器一般用二进制译码器实现:

七、显示译码器

八、译码器应用

译码器实现组合逻辑函数

第二个怎么实现的我还有点没搞明白。

九、数据选择器

数据选择器:从多路数据输入中选择其中一路送到输出端。

A1A0为地址信号,也就是说A1A0的二进制组成的数值就是要选择的地址,选择的地址的内容就是F的输出。在此题中为D3

4选1数据选择器真值表

4选1数据选择器真值表

8选1数据选择器真值表

2片的4选1实现8选1

——思路1:加使能端

使能端是芯片的一个输入引脚,或者电路的一个输入端口,只有该引脚激活,芯片才能工作,通常情况下为高电平有效,若符号上面有一横,则表示低电平有效。

最高位设置为使能输入:A2控制1号还是2号的开启

——思路2:

1.用数据选择器实现组合逻辑函数

思路:利用地址变量产生所有的最小项,通过输入信号Di的不同取值,选取组成逻辑函数所需的最小项。

第一种题型(最简单)

第二种题型(进阶)

第三种题型(终极)

问:数据选择器和二进制译码器都可以实现组合逻辑函数,它们的设计方法有何不同?

答:数据选择器可以有多个输入一个输出,而二进制译码器相反

再来一个易混淆的:

十、加法器

半加器和全加器

全加器:

-

串行进位加法器:

特点:结构简单;运算速度慢。 -

超进位加法器:

加法器应用

- 用4位加法器将8421BCD码转换为余3码

- 8421BCD码是二进制编码的十进制数;BCD码与十进制数的转换。将十进制数75.4转换为BCD码如:75.4=(0111(0101.0100)BCD

- 余3码是一种 BCD码 ,它是由8421码加3后形成的(即余3码是在8421码基础上每位十进制数BCD码再加上二进制数0011得到的)。

- 用加法器实现减法运算

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)