实验8:4位行波加法计数器

本次实验我们学会了怎么去实现T触发器和行波加法计数器。异步行波加法计数器是一种数字电路设计,用于实现计数功能。它的工作原理是通过级联多个触发器来实现二进制计数。异步行波加法计数器的优点包括:1. 简单:异步行波加法计数器的设计相对简单,只需要级联多个触发器即可实现计数功能。2. 高速:由于异步行波加法计数器没有时钟信号的限制,每个触发器可以独立地响应输入信号的变化,从而实现高速计数。(这里是相对于

实验目的

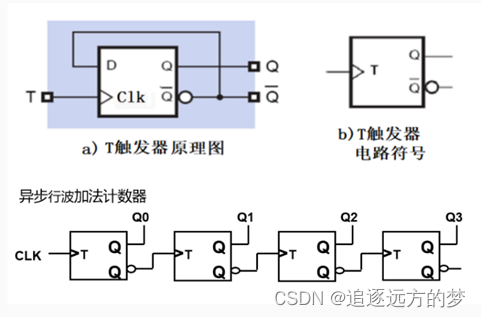

首先实现T触发器(可以利用Logisim库中的D触发器),然后利用T触发器实现一个4位的2进制加法计数器。计数器的输入信号为CLK,输出信号为Q0、Q1、Q2、Q3。

实验原理:

4位行波加法计数器是一种数字电路,用于计数或累加二进制数。它由4个触发器组成,每个触发器都是一个单独的存储单元,可以存储一个比特(0或1)。

工作原理如下:

1. 初始状态下,计数器的输出为二进制数0000,即所有的触发器都置为0。

2. 当计数器接收到一个时钟信号时,触发器开始工作。

3. 触发器根据其输入信号和之前的状态决定是否进行状态转换。当时钟信号的上升沿到来时,触发器会根据输入信号的变化来决定是否改变输出状态。(也可以设置为下降沿)

4. 计数器的最低位触发器(即第一个触发器)在每个时钟周期中都会进行状态转换。当最低位触发器发生变化时,代表计数器发生了加1的操作。

5. 如果最低位触发器在变化的操作中,产生了进位(carry)现象,则触发器会将进位信号传递给下一个高位触发器,并且该高位触发器也会进行状态转换。

6. 这样,当上一位触发器发生进位时,下一位触发器也会被激活,从而实现二进制数的累加。

7. 当所有的触发器都完成状态转换后,计数器的输出就对应着当前的计数值。

如:0000-0001-0010-0011-0100-0101-0110-0111-1000-1001-1010-1011-1100-1101-1110-1111。通过这种方式,4位行波加法计数器就可以实现二进制数的计数和累加功能。它适用于各种计数应用,例如频率分频、计时器等。

T触发器是一种基本的数字逻辑电路元件,也被称为“翻转-翻转器”或“T型翻转器”。它是由触发器门电路组成的,用于存储和操作二进制数据。

T触发器有两个输入端:时钟输入(CLK)和T输入。它有两个输出端:Q和~Q。T触发器的工作原理如下:

1. 当时钟输入(CLK)为高电平时,T触发器处于工作状态。

2. 当T输入为低电平时,T触发器保持其当前状态,不发生变化。

3. 当T输入为高电平时,T触发器的输出(Q)会根据时钟信号的上升沿或下降沿来改变。

4. 当时钟信号的上升沿到来时,如果T输入为高电平,则T触发器的输出(Q)会翻转为相反的状态。如果之前输出为低电平,则翻转为高电平;如果之前输出为高电平,则翻转为低电平。

5. 当时钟信号的下降沿到来时,如果T输入为高电平,则T触发器的输出(Q)保持不变。

输入T可以认为是~Q;(非Q);(因而T触发器可以由D触发器改装得到,将D触发器的输出端~Q连到输入T端。)

T触发器可以用于实现各种数字逻辑功能,如计数器、频率分频器、状态存储器等。它的特点是可以根据时钟信号的变化来触发状态的改变,从而实现数据的存储和操作。

有时也认为CLK端是T端,不过无伤大雅。

实验过程:

- T触发器

利用已有的D触发器实现T触发器如下:

将时钟信号设置为高电平,发现Q输出变为1,~Q保持0不变;

将时钟信号改为低电平,输出保持不变;

时钟信号再次达到了高电平,Q变为了0,~Q变为了1

时钟信号变为0,输出保持不变

这样,我们就得到了一个T触发器;

- 异步行波加法计数器

下面,我们利用上面的T触发器来实现计数器;

利用4个T触发器来实现4位二进制行波加法计数器,计数容量为16;

每个T触发器的Q端接输出,从Q0到Q3位数依次递增,最低位为Q0;

~Q端接下一个T触发器的时钟信号端,

当Q0的~Q端由0变为1时,相当于Q1的时钟周期的上升沿到来,从而引起Q1的改变。比如初始输出0000,当时钟信号上升沿第一次到来后,Q0变为1,~Q0,~Q1,~Q2,~Q3都为0,此时输出0001;当时钟信号的上升沿第二次到来后,Q0变为0,~Q0变为1,从而Q1变为1,输出变为0010;以此类推……

继续改变CLK

将其封装为子电路有:

测试结果:

经测试,上述结果正确。

总结与思考:

本次实验我们学会了怎么去实现T触发器和行波加法计数器。

异步行波加法计数器是一种数字电路设计,用于实现计数功能。它的工作原理是通过级联多个触发器来实现二进制计数。

异步行波加法计数器的优点包括:

1. 简单:异步行波加法计数器的设计相对简单,只需要级联多个触发器即可实现计数功能。

2. 高速:由于异步行波加法计数器没有时钟信号的限制,每个触发器可以独立地响应输入信号的变化,从而实现高速计数。(这里是相对于同步加法计数器来说)

{对于异步行波加法计数器来说,相对于同步计数器而言,它的计数速度可能会很慢。

异步行波加法计数器的计数速度受到触发器的响应时间和传播延迟的影响。由于每个触发器都是独立工作的,当输入信号变化时,触发器需要一定的时间来响应并传递信号。这个传播延迟会导致计数器的输出信号在时间上有所偏移。

相比之下,同步计数器在计数过程中会受到时钟信号的同步控制,所有的触发器在时钟的上升沿或下降沿同时进行状态更新,因此同步计数器的计数速度更快。

然而,需要注意的是,异步行波加法计数器的高速性是相对于其他异步计数器而言的。在某些特定的应用场景下,异步行波加法计数器可能仍然可以提供足够的计数速度。}

3. 灵活性:异步行波加法计数器可以根据需要自由选择计数的位数,可以实现不同位数的计数功能。

然而,异步行波加法计数器也存在一些缺点:

1. 稳定性:由于异步行波加法计数器的触发器是独立工作的,输入信号的变化可能会导致计数器的不稳定状态。这可能会导致计数器出现错误的计数结果。

2. 同步问题:异步行波加法计数器的各个触发器在计数过程中可能会有不同的延迟,这可能导致计数器的输出信号不同步。

3. 复杂性:随着计数位数的增加,异步行波加法计数器的设计和布线会变得更加复杂,增加了设计和调试的难度。

综上所述,异步行波加法计数器在一些特定的应用场景下具有一定的优势,但在一些对稳定性和同步性要求较高的应用中可能不适用。在实际应用中,需要根据具体需求综合考虑其利弊,并选择合适的计数器设计方案。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

所有评论(0)