【AD24报错】PCB调整线宽后提示 Width Constraint: Track ### on Top Layer的解决方案

Width Constraint 的意思是宽度约束,往往是布线的规则限制所导致。可能在设计中设置了多个相互冲突的线宽规则。例如,为不同的网络或层设置了不同的最小线宽和最大线宽要求,但在实际布线过程中,某些走线无法同时满足这些规则,从而导致报错。比如,为电源网络设置了较宽的最小线宽要求,而同时为一些信号网络设置了较窄的线宽限制,当这两种网络在某个区域交叉或靠近时,可能会出现无法满足所有线宽规则的情况

【AD24报错】PCB调整线宽提示Width Constraint: Track(##mil, ##mil)(##mil, ##mil)on Top Layer的解决方案

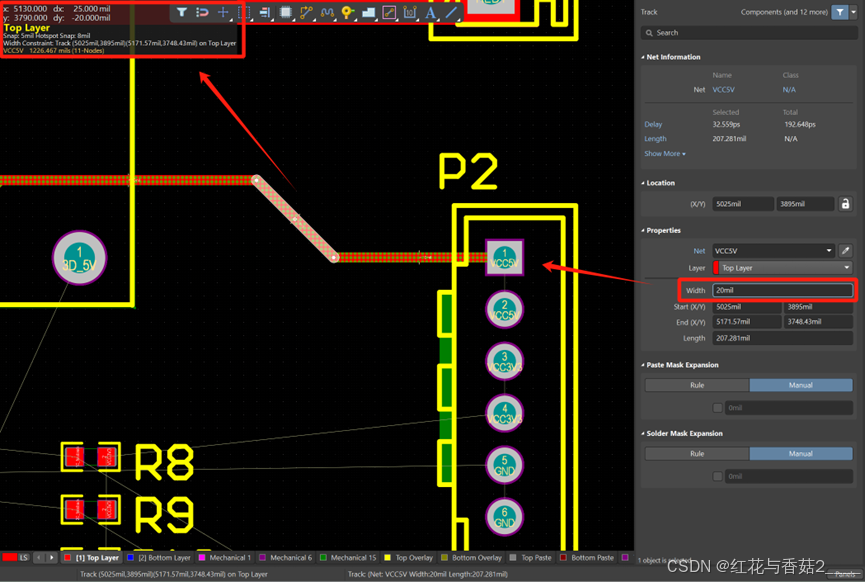

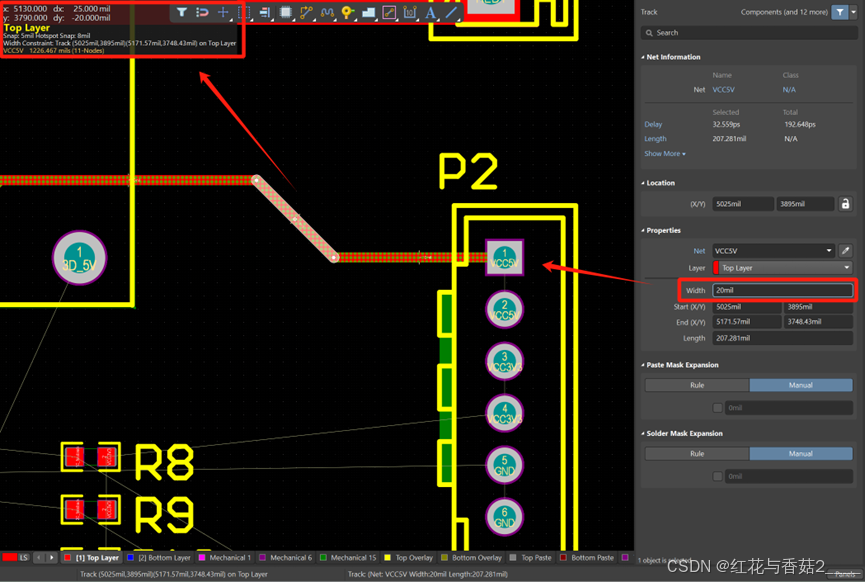

一、Width Constraint问题复现

在调整线宽后,系统报错:

Width Constraint: Track (5025mil,3895mil)(5171.57mil,3748.43mil) on Top Layer

Width Constraint 的意思是宽度约束,往往是布线的规则限制所导致。可能在设计中设置了多个相互冲突的线宽规则。例如,为不同的网络或层设置了不同的最小线宽和最大线宽要求,但在实际布线过程中,某些走线无法同时满足这些规则,从而导致报错。比如,为电源网络设置了较宽的最小线宽要求,而同时为一些信号网络设置了较窄的线宽限制,当这两种网络在某个区域交叉或靠近时,可能会出现无法满足所有线宽规则的情况。

另一方面,全局与局部规则不一致,AD 允许设置全局线宽规则和针对特定区域、网络或元件的局部线宽规则。如果全局规则和局部规则之间存在不一致,可能会引发报错。例如,全局线宽规则设置为所有走线最小线宽为 10mil,但在某个特定的高速信号网络上设置了局部线宽规则为 5mil,当对该网络进行布线时,可能会与全局规则冲突而报错。

二、有关于Width Constraint的解决方案

- 打开 PCB 文件后,在菜单栏中选择 【设计】-【规则】。

- 在弹出的 “PCB 规则及约束编辑器” 对话框中,展开左侧的 “Routing”(布线)选项。点击 “Width”(线宽)选项,此时在右侧会显示当前的线宽规则设置。

- 若要修改所有线宽的规则,可以直接在 “约束” 列表中修改 “最小宽度”“最大宽度” 和 “首选宽度” 的值。

- 如果想针对特定的网络或层设置不同的线宽规则,可以点击下方的 “添加” 按钮,在弹出的对话框中选择规则的适用范围,如特定的网络、特定的层等,然后设置相应的线宽值。

- 修改完成后,点击 “确定” 按钮保存规则设置。

三、可能导致 Width Constraint 报错的其他因素(供参考)

- 手动布线错误:

在手动布线时,可能由于疏忽或操作不当,导致走线的线宽不符合设计规则。例如,在调整走线时不小心将线宽设置为错误的值,或者在连接不同网络时没有注意线宽的要求。比如,在连接两个元件时,为了快速完成布线,随意选择了一个不合适的线宽,而这个线宽与设计规则中的要求不符。 - 自动布线结果不符合规则:

使用自动布线工具时,可能会出现自动生成的布线结果不符合线宽约束的情况。自动布线工具通常会根据设计规则进行布线,但在复杂的设计中,可能由于各种因素无法完全满足所有规则。例如,在高密度的 PCB 设计中,自动布线工具可能会为了找到可行的布线路径而选择了不符合线宽要求的走线方式。 - 元件引脚线宽不匹配:

如果元件封装中的引脚线宽与设计规则中的线宽要求不匹配,可能会在连接元件时导致线宽约束错误。例如,元件封装的引脚线宽设置为较窄的值,而设计规则要求连接该引脚的走线必须具有较宽的线宽。这种情况下,在将元件放置到 PCB 上并进行布线时,就可能会出现线宽不一致的问题而报错。 - 库文件中的错误:

PCB 设计中使用的元件库文件可能存在错误,导致线宽约束错误。例如,库中的元件封装定义的线宽与实际设计要求不符,或者库中的设计规则与当前项目的设计规则不一致。当从库中调用元件进行设计时,如果没有仔细检查元件的属性和库文件的规则,就可能会出现线宽错误。

最后,欢迎交流学习。

解决方案与项目截图为作者原创,转载请标明出处。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)