VHDL语言基础-状态机设计-ASM图法状态机设计

VHDL语言基础-状态机设计-ASM图法状态机设计

目录

有限状态机的描述方法:

ASM图:

ASM本质上是一个有限状态机,主要用于同步时序系统。

ASM精确地表示出状态转换的时间关系。

从形式上看,这种流程图类似于描述软件程序的流程图,但它能和实现它的硬件很好的对应起来。

状态转移图:

状态转移列表:

| 状态 \ 输入 | a=‘1’ | b=‘1’ | default |

| S0 | S1 | S2 | |

| S1 | S2 | S0 | |

| S2 | S0 |

MDS图:

ASM图法状态机设计:

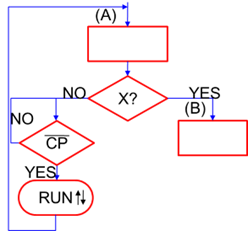

ASM图的组成:

状态框:

用一个矩形框来表示一个状态。状态的名称写在左上角;状态的二进制编码写在右上角;操作内容写在矩形框内。在同步系统中,状态经历的时间至少是一个时钟周期,也可以是几个周期。

判断框:

用单入口双出口的菱形或单入口多出口的多边形符号表示。在菱形和多边形框内写检测条件,在分支出口处注明各分支所满足的条件。

判断框必须跟着状态框。判断框的执行与状态框在同一时钟周期内。

条件框:

用椭圆框表示。条件框一定是与判断框的一个转移分支相连接,仅当判断框中判断变量满足相应的转移条件时,才进行条件框中标明的操作和信号输出。

虽然条件框和状态框都能执行操作和输出信号,但二者有很大区别

状态框与条件框的区别:

状态单元:

状态单元由一个状态框或 条件框组成。状态单元的入口必须是状态框的入口,出口可以有几个,但必须指向状态框。

仅包含一个状态框,无判断框和条件框的ASM块是一个简单块。

每个状态单元表示一个时钟周期内系统所处的状态,在该状态下完成快内的若干操作。

用ASM图描述一个系统控制器时,实际上是描述了该控制器的硬件结构和时序工作过程,因此ASM图与硬件有很好的对应关系,ASM图的硬件实现有以下几种方法:

用计数器实现ASM图

用多路选择器实现ASM图

每个状态一个触发器(定序型)

基于ROM法实现ASM图(微程序型)

用计数器实现ASM图:

ASM图的状态分配:

N个状态变量可以描述2^n个状态。该ASM图中有3个状态,所以需要两个状态变量。设两个状态变量为Q2Q1,我们选用2个D触发器。用二进制计数序列依次表示状态。

状态转换表:

因为10和11状态与输入X无关,所以X值可作任意值处理。

表中01未指定状态,采用计数器实现,因此需考虑因偶然因素出现01状态时,应强迫其次态为00,所以一旦出现01状态后,经过一个时钟周期就可以自动回到有用状态循环。

| 现态 | 次态 | 输出 | ||||

| Q2 | Q1 | X | Q2n+1 | Q1n+1 | Z1 | Z2 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | X | 0 | 0 | 0 | 0 |

| 1 | 0 | X | 0 | 0 | 0 | 0 |

| 1 | 1 | X | 0 | 0 | 0 | 0 |

由状态转换表推导触发器的驱动方程:

对于复杂的ASM图和相应的状态表可用卡诺图对次态进行化简,得到简化的驱动方程。

ASM图除了可以得到状态表和驱动方程外,还可以得到输出方程

ASM图的硬件实现:

采用计数器法实现ASM图,一旦ASM图有很小的改动,就需要重新设计与次态相关的组合电路部分。此外,当系统的状态超过8个时,ASM图的硬件实现也很复杂。

举例:

要求设计一套交叉路口交通信号灯,该路口有一条交通干线与支线,支线上装有传感器,当支线有车通过时,传感器输出信号CAR=1。正常的工作状态时干线亮绿灯,支线亮红灯;当CAR=1时,干线亮红灯,支线亮绿灯,并开始计时,START_TIEMR=1,当计时结束,即信号TIMED=1时,重新回到正常工作状态(干线亮绿灯,支线亮红灯)。

有限状态机的分类:

从信号输出方式上分:

Mealy型状态机

Moore型状态机

从结构上分:

单进程状态机

两进程状态机

三进程状态机

从表达方式上分:

符号化状态机

确定状态编码状态机

顺序编码状态机

独热码状态机

格雷码状态机

从信号输出方式上分:

Moore型有限状态机:

是指那些输出信号仅与当前状态有关的有限状态机,即可以把Moore型有限状态机的输出看成是当前状态的函数。

Moore型有限状态机框图:

Mealy型有限状态机:

是指那些输出信号不仅与当前状态有关,而且还与所有的输入信号有关的有限状态机,即可以把Mealy有限状态机的输出看作当前状态和所有输入信号的函数。可见,Mealy有限状态机要比Moore有限状态机复杂一些。

Mealy有限状态机框图:

Moore型和Mealy型有限状态机的区别:

Moore型有限状态机仅与当前状态有关,而与输入信号无关;Mealy型有限状态机不但与当前状态有关,而且还与状态机的输入信号有关。

采用何种有限状态机的判别条件:

Moore型有限状态机可能要比相应的Mealy型有限状态机需要更多的状态。

Moore型有限状态机的输出与当前的输入部分无关,因此当前输入产生的任何效果将会延迟到下一个时钟周期。可见,Moore型状态机的最大优点就是可以将输入部分和输出部分隔离开。

对于Mealy型有限状态机来说,由于它的输出是输入信号的函数,因此如果输入信号发生改变,那么输出可以在一个时钟周期内发生改变

从状态机的结构上分:

单进程描述:

它就是将状态机的三个逻辑单元(状态寄存器、下状态产生逻辑、输出逻辑)合并起来,采用一个进程描述。

适用于简单的设计;

对于复杂的状态机,可读性差,易出错,不利于EDA软件优化。

单进程状态变量可以定义为变量类型,放在进程的说明部分;

一般在进程的开头写上时钟有效边沿的检测语句;

注意在这里进程敏感参数表中的car和timed可省去

rising_edge(clock)也可以写成clock’event and clock=‘1’;

条件涵盖不完整的if语句会产生寄存器;

这是将时序电路和组合电路混合的系统,有时会引入不必要的寄存器。如果将描述时序的部分放在具有边沿检测条件的if语句或wait语句的进程中,而将描述组合电路的语句放在普通的进程中,这样可以有效控制寄存器的引入。

双进程状态机:

双进程中状态变量要定义为SIGNAL类型,用于进程间信息的传递

可以在产生寄存器的进程中加上异步复位语句,用于确定初始状态

seq: PROCESS (clock)

BEGIN

IF reset=‘1’ THEN pr_state <= G;

IF(rising_edge(clock)) THEN

pr_state <= next_state;

END IF;

END PROCESS seq;

注意在组合进程中if语句要写完整if-else

三进程状态机:

op进程也可以用并行语句改写:用并行语句改写,不能再使用进程

描述状态寄存器的时序进程

描述下状态产生逻辑的组合进程

定义输出的组合逻辑进程

使用三进程描述状态机,可以达到很好的综合效果。

从表达方式上分:

符号化状态机:

所谓符号化状态机,就是在程序的说明部分使用TYPE语句定义枚举类型,其元素用状态机的状态名来定义。状态变量(如状态机的现态和次态)定义为变量或信号,并将状态变量的数据类型定义为含有既定状态元素的枚举类型。

在使用多进程时,为便于信息传递,要将状态变量定义为信号。

前面的三种进程描述状态机的例子中,都是使用符号化状态机的表达方式。

符号化状态机——类型定义语句:

确定状态编码状态机:

使用符号化定义的枚举类型,枚举类型文字元素的编码通常是自动设置的,综合器根据优化情况、优化控制的设置或设计者的特殊设定来确定各元素具体编码的二进制位数、数值及元素间编码的顺序。

也可以在程序中指明编码方式。

常用的编码方式:2进制编码、格雷码编码、One-hot编码

确定状态编码状态机——2进制编码:

状态机的每一个状态用二进制位来编码

例:实现4状态的状态机,其其二进制编码可为 状态1=“00”状态2=“01”状态3=“10”状态4=“11”

需要的寄存器数量最少,有n个寄存器就可以对2^n个状态进行编码。

需要更多的外部辅助逻辑,并且速度较慢。

确定状态编码状态机——格雷码编码:

格雷码编码每次仅一个状态位的值发生变化

例:实现4状态的状态机,其格雷码编码可为 状态1=“00”状态2=“01”状态3=“11”状态4=“10”

特点:触发器使用较少,速度较慢,不会产生两位同时翻转的情况。当状态位的输出被异步应用时,格雷码编码是有益的。

确定状态编码状态机——One-hot编码:

One hot的编码方案对每一个状态采用一个触发器,即4个状态的状态机需4个触发器。同一时间仅1个状态位处于有效电平(如逻辑“1”)

例:实现4状态的状态机,其one hot编码可为 状态1=“0001”状态2=“0010”状态3=“0100”状态4=“1000”

特点:触发器使用较多,但逻辑简单,速度快

关于one-hot、gray-code、binary编码使用说明:

Binary、gray-code编码使用较少的触发器,较多的组合逻辑,而one-hot编码反之。由于CPLD更多的提供组合逻辑,而FPGA更多的提供触发器资源,所以CPLD多使用gray-code,而FPGA多使用one-hot编码。

对于小型设计使用gray-code和binary编码更有效,而大型状态机使用one-hot编码更有效

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)