使用N-MOSFET实现浪涌电流抑制

所以,我们可以发现,方案A/C就是基于P-MOSFET的浪涌电流抑制电路,放置的位置是电源线的正极,也就是通常所谓的“高边”。本文将要更新的方案E/F就是基于N-MOSFET的浪涌电流抑制电路,放置的位置是电源线的负极,也就是通常所谓的“低边”。综合来看,在4类浪涌电流抑制电路中,基于P-MOSFET的A/C方案,基于N-MOSFET的E/F方案,并无优劣之分,只是各自的应用场景有所差异。图5.8

1. 简介

如下所示给出了基于P-MOSFET的四种浪涌电流抑制方案:

图5.78 Single P-MOSFET负载开关电路方案A 图 5.80 Single P-MOSFET负载开关电路方案B

图 5.80 Single P-MOSFET负载开关电路方案B 图 5.81 Single P-MOSFET负载开关电路方案C

图 5.81 Single P-MOSFET负载开关电路方案C 图 5.82 Single P-MOSFET负载开关电路方案D

图 5.82 Single P-MOSFET负载开关电路方案D

后来经过自己的study以及工程师朋友的讨论,方案B和D应用于浪涌电流抑制,有所不妥;主要原因是:在VIN上电的瞬间且Q2/Q4完全导通之前,给输出电容C9/C10/C19/C20充电的浪涌电流会“部分”或“完全”从体二极管流过。

也许有人会问,这样的电路是否会存在P-MOSFET因上电瞬间的浪涌电流而损坏的可能?答案是,在合适选择了P-MOSFET连续漏源电流的情况下,通常不会导致管子损坏。这点,我们后续文章再单独分析。

2. 更新方案

PNP三极管适合做“高边开关”,NPN三极管适合做“低边开关”,这是由它们的结构或导通关断特性决定的。类似的结论是,P-MOSFET适合做“高边开关”,N-MOSFET适合做“低边开关”(如同步BUCK电路的low-side switch就是N-MOSFET)。

所以,我们可以发现,方案A/C就是基于P-MOSFET的浪涌电流抑制电路,放置的位置是电源线的正极,也就是通常所谓的“高边”。本文将要更新的方案E/F就是基于N-MOSFET的浪涌电流抑制电路,放置的位置是电源线的负极,也就是通常所谓的“低边”。

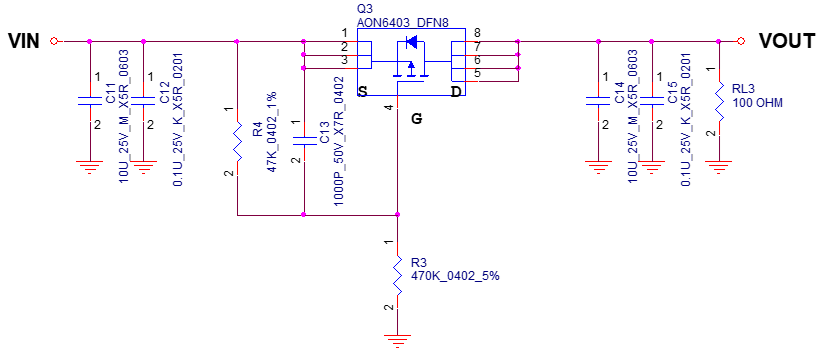

图5.83 基于N-MOSFET的浪涌电流抑制电路方案E

图5.83所示,方案E适合VCC电源范围不超过Vgs(Gate-to-Source Voltage)的应用场景。

图5.84 基于N-MOSFET的浪涌电流抑制电路方案F

图5.84所示,方案F适合VCC电源范围超过Vgs的应用场景,此时在C18上并联电阻R6,使R6与R5组成分压电路,保证Q4栅极-源极电压不超过其Vgs范围。

3. 分压电阻值的说明

图 5.81 Single P-MOSFET负载开关电路方案C

图 5.81 Single P-MOSFET负载开关电路方案C

图5.81所示,当输入电源VIN大于AON6403元件的栅极和源极耐压值±20V,达到60V甚至100V时,可以通过增加R3电阻抬升栅极电压,使得栅极和源极之间的差值保持在20V以内。当VIN = 60V时,栅极和源极之间差值为VGS = 60V * 47k / ( 470k + 47k ) = 5.45V;当VOUT = 100V时,栅极和源极之间差值为VGS = 100V * 47k / ( 470k + 47k ) = 9.09V;可见,5.45V和9.09V都是在±20V耐压范围内的,是安全的。有人提出,是否需要将R3=470k电阻和R4=47k电阻位置互换,才能满足上述两个计算结果5.45V和9.09V?

答案是,不需要。上述两个算式分子上的阻值使用的是R4=47k,这样可以直接得到源极和栅极之间的差值VGS。

如果使用通常的分压公式计算是,当VIN = 60V时,栅极的电压为Vg = 60V * 470k / ( 470k + 47k ) = 54.54V,那么源极与栅极之间的差值为VGS = 60V - 54.54V = 5.46V,殊途同归;当VIN = 100V时,同理。

图5.84 基于N-MOSFET的浪涌电流抑制电路方案F

图5.84所示,在方案F中,取VCC = 60V,N-MOSFET Q4栅极和源极之间的差值,也是可以直接计算的,即 VGS = 60V * 47k / ( 470k + 47k ) = 5.45V。

4. 总结

综合来看,在4类浪涌电流抑制电路中,基于P-MOSFET的A/C方案,基于N-MOSFET的E/F方案,并无优劣之分,只是各自的应用场景有所差异。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)