DDR协议基础进阶(四)DDR协议命令波形时序一——(ACT、Read、Write)

1. AL = 0时场景,易导致总线上的DQ数据输出时,产生气泡Bubble,打断数据传输的连续性,降低数据传输效率;也可能会推迟总线上DQ数据的发出时间导致,Latency增加,降低传输效率。参考:https://blog.csdn.net/Rspate/article/details/107859785。: RAS to CAS Delay,RAS至CAS延迟;亦即从ACT到RD/WR命令之间

DDR协议基础进阶(四)DDR协议命令波形时序一——(ACT、Read、Write)

一、DDR 命令真值表

- DDR的Command命令由CKE、CS#、RAS#、CAS#、WE#信号组成,这几个信号进行不同的搭配组合会形成不同的Command命令模式;(RAS: Row Address Strobe,行地址选通脉冲;CAS: Column Address Strobe,列地址选通脉冲;)

- Command命令与地址Address相互协同共同完成对DDR mem颗粒的访问操作。

二、ACT激活命令时序要求

ACTIVE命令是在对mem颗粒进行读写访问之前需要发出的第一个命令:

- ACTIVATE命令协同Address命令会激活某一特定bank的某一行,每一次操作只能打开同一个Bank的一行,而非多行;

- Address选中激活的行,只有在Precharge之后才会失效。

- 传输过程中Burst Length模式在MR0寄存器中定义,分三种:BL8 fixed,BC4 fixed,BL8 or BC4 on the fly。

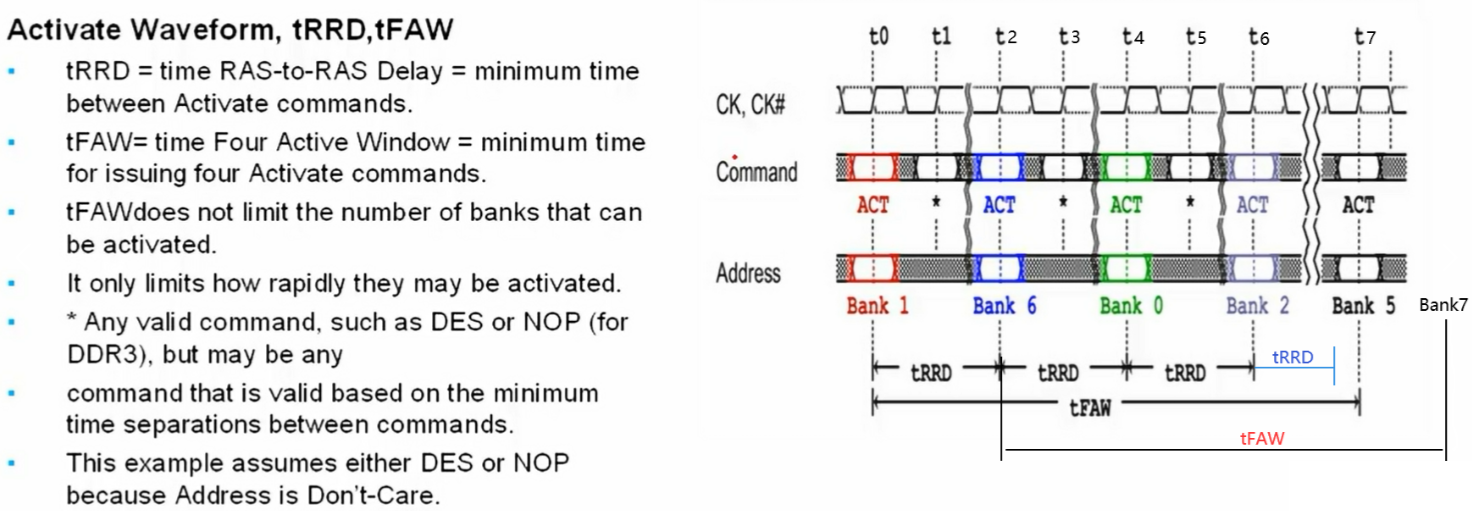

2.1、ACTIVATE波形——tRRD、tFAW

- t0-t7:激活Bank中的某一行;

- tRRD:激活两个不同Bank所需要的最小时间间隔;

- tFAW:连续激活五个不同Bank所需要的时间间隔(注意:tFAW > 4 * tRRD),其中tFAW是滚动计时,并不会限制Bank数量。

2.2、ACTIVATE波形——tRAS、tRC

- t0-t10:ACT激活和Precharge关闭协同操作特定Bank中的某一行;

- tRRD:激活两个不同Bank所需要的最小时间间隔;

- tRAS:ACT激活Bank的某一行后,再对其进行Precharge关闭所需要的最小时间间隔;

- tRC:同一块Bank先后被打开所需要的最小时间间隔,第一次ACT打开Bank后需要先Precharge关闭然后再次执行ACT打开操作(两次ACT打开的同一块Bank的不同Row);

- tRD:非同一块Bank先后被打开所需要的最小时间间隔,第一次ACT打开Bank后需要先Precharge关闭然后再次执行ACT打开操作;

- tRP:关闭Precharge Bank所需要消耗的时间。

三、Read命令时序要求

当ACTIVE命令发出并激活Address指定的Bank的某一Row行之后,随即开始进行Read读访问:

- 读数据访问的地址一般为A0-Ax,其中A10被用来判断是否需要进行Auto-precharge操作;

- 下图中的**CAS Latency(CL)**在MR0寄存器中进行配置,**Additive Latency(AL)**在MR1寄存器中进行配置。

3.1、Read 波形——无Additive Latency

- tRCD: RAS to CAS Delay,RAS至CAS延迟;亦即从ACT到RD/WR命令之间的时间间隔。

- 最小的延迟时间需满足:CL = nRCD = nRP = 8个时钟周期。

- 读取数据:先ACT行地址 —> 发出读命令和列地址 —> 等待列地址生效后开始数据读取。

3.2、Read 波形——有Additive Latency

- AL的值是通过配置MR1寄存器实现,当AL的值不为0时,ACTBank后,RD读命令会提前发出,但是并不会影响正式读取数据的时间节点,AL=0和AL=7的时序都是在t16时刻开始进行数据读取。

3.3、Read 波形——Additive Latency使用场景

1. AL = 0时场景,易导致总线上的DQ数据输出时,产生气泡Bubble,打断数据传输的连续性,降低数据传输效率;也可能会推迟总线上DQ数据的发出时间导致,Latency增加,降低传输效率。

-

tRRD:激活两个不同Bank所需要的最小时间间隔;

-

tRCD: RAS to CAS Delay,RAS至CAS延迟;亦即从ACT到RD/WR命令之间的时间间隔;

-

tRAS:ACT激活Bank的某一行后,再对其进行Precharge关闭所需要的最小时间间隔;

2. AL ≠ 0时场景,可以ACT激活Bank后,快速发出对应的RDA读指令,从而避免不同Bank之间的ACT和RDA命令 ‘冲突’,避免数据传输时产生Bubble,提高DQ的连续性,大大提高数据传输效率。

3.4、Read to Precharge波形

- tRTP:发出READ读命令后再对当前Bank进行Precharge操作所需要的最小时间间隔;

- tRP: Precharge command period,预充电有效周期,即关闭Bank所需要的最小时间,在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行;

3.5、Sequential Read波形——BC4 to BC4

- tCCD:连续READ(WRITE)读取两个Bank的最小时间间隔;

3.6、Sequential Read波形——BL8 to BL8

- 与BL8 to BL8传输相比,BC4 to BC4传输会减少DQS信号的翻转,降低功耗,但是对于数据传输效率的提升并无帮助。

3.7、Read to Write波形——BL8 to BL8(重要)

- tRL:从发出READ读命令到DQ正式开始进行读数据之间的最小时间间隔;

- tWL:从发出WRITE写命令到DQ正式开始进行写数据之间的最小时间间隔;

- 2tCK:DQ输出READ数据转换为输出WRITE需要消耗的最小时间,这里的消耗不可避免,且会造成一定的效率损失。

3.8、Read to Write波形——BC4 to BC4

- On The Fly(OTF)的传输模式对效率的提升有一定的帮助;(如果数据在传输的最后一拍只传输BC4,则会节省2个clk cycle)

3.9、Read to Write波形——BL8 to OTF(BC4)

- 在实际的DDR工作过程中,不同的工作模式(Burst type)不可以随便的进行切换,这里的时序只作为了解,实际场景中少见。(初始化过程中只能进行一种工作模式的设置)

- 本节时序同3.6小节。

四、WRITE命令时序要求

WRITE命令同READ命令相似,WRITE命令也需要在ACTIVE命令发出并激活Address指定的Bank的某一Row行之后发出,不同之处在于WRITE命令发出时会伴随DM信号以控制数据的Enable或者masked。当DM信号为高时,DQ数据无效;当DM信号为低时,DQ数据有效。 - 写数据访问时地址中A10也会被用来判断是否需要进行Auto-precharge操作。

4.1、Write波形——BL8

- tRCD: RAS to CAS Delay,RAS至CAS延迟;亦即从ACT到RD/WR命令之间的时间间隔。

- tWL:从发出WRITE写命令到DQ正式开始进行写数据之间的最小时间间隔;

4.2、Write to Precharge波形——BC4

- tWR:写恢复时间,即写数据完成后到发出预充电命令之间所需时钟周期,写突发之后一定要跟随一个预充电命令;

4.3、Write to Precharge波形——OTF(BC4)

- 在Burst Length为OTF模式下,tWR的计时起点应该以BL8模式时开始计数;

4.4、Sequential Write波形——BL8 to BL8

- tCCD:连续WRITE(READ)写入两个Bank的最小时间间隔,其值为4;

4.5、Write to Read波形——BC4 to BC4

- tWTR:从DQ写完数据之后开始到发出读命令之间的延时;

- tWTR的计时起点以BL4模式执行;

4.6、Write to Read波形——BL8 to OTF(BC4/BL8)

- tWTR的计时起点以BL8模式执行;

4.7、Write to Write波形——BC4 to OTF(BC4)

- 完成数据传输的时钟周期同4.9节的时序一致;

4.8、Write to Write波形——BL8 to BL8

参考:https://www.sohu.com/a/163865810_781333

参考:https://blog.csdn.net/Rspate/article/details/107859785

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献21条内容

已为社区贡献21条内容

所有评论(0)