计算机组成原理 第四章 存储器 Part3 单体多字/多体并行/双端口/四体交叉存储器题目

1:由于采用的是四体低位交叉存储器,所以在第一轮读取连续6个地址单元的时候,花费6×T4𝑇4时间,但开始第二轮的时候,由于M1模块还在占用中,需要再经历T2𝑇2时间,才能进行下一轮新的读取(再次进入下一轮的时候不需要第6个字读取结束,第5个读取结束,M1就空出来了,即可马上进入下一轮),中间的每一轮都不需要等待,最后一轮后读取完第二个M2后,还有半个T2𝑇2时间,所以答案是(80-1)×2T

1.提高访存速度的措施

1.采用高速器件

2.采用层次结构:Cache -主存

3.调整主存结构

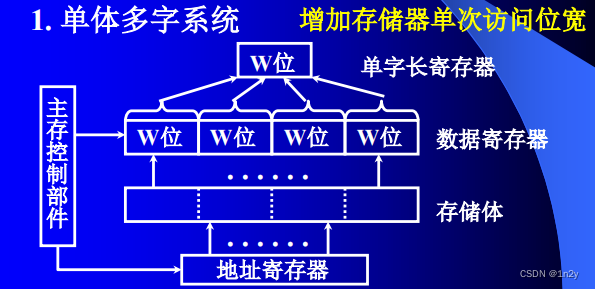

1)单体多字系统 增加存储器单次访问位宽

单体多字系统的特点是存储器中只有一个存储体,每个存储单元存储m个字,总线宽度也为m个字。一次并行读出m个字,地址必须顺序排列并处于同一存储单元。

单体多字系统在一个存取周期内,从同一地址取出m条指令,然后将指令逐条送至CPU执行,即每隔1/m存取周期,CPU向主存取一条指令。这显然提高了单体存储器的工作速度。

缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或操作数不能连续存放,这种方法的效果就不明显。

2) 多体并行系统

高位交叉 实际上是顺序存储

各存储体顺序编址

高位地址表示体号,低位地址为体内地址。如图所示,存储器共有4个模块M0~M3,每个模块有n个单元,各模块的地址范围如图中所示。

特点:

- 高位交叉方式下,总是把低位的体内地址送到由高位体号确定的模块内进行译码。

- 顺序串行存取。访问一个连续主存块时,总是先在一个模块内访问,等到该模块访问完才转到下一个模块访问,CPU总是按顺序访问存储模块,各模块不能被并行访问,因而不能提高存储器的吞吐率。

低位交叉 各存储体交叉编址

在不改变存取周期的前提下,增加存储器带宽

低位地址为体号,高位地址为体内地址。

每个模块按“模m”交叉编址,模块号=单元地址%m,假定有m个模块,每个模块有k个单元,则0,m,…,(k-1)m单元位于M0;第1,m+1,…,(k-1)m+1单元位于M1;以此类推。

特点:

- 低位交叉方式下,总是把高位的体内地址送到由低位体号确定的模块内进行译码。

- 程序连续存放在相邻模块中,因此称采用此编址方式的存储器为交叉存储器。

- 采用低位交叉编址后,可在不改变每个模块存取周期的前提下,采用流水线的方式并行存取,提高存储器的带宽。

设模块字长等于数据总线宽度,模块存取一个字的存取周期为T,总线传送周期为r,为实现流水线方式存取,存储器交叉模块数应大于等于

式中,m称为交叉存取度。每经过时间延迟后启动下一个模块,交叉存储器要求其模块数必须大于等于m,以保证启动某模块后经过m×r的时间后再次启动该模块时,其上次的存取操作已经完成(即流水线不间断)。这样,连续存取m个字所需的时间为

而顺序方式连续读取m个字所需的时间为。可见低位交叉存储器的带宽大大提高。

2. 双端口RAM

双端口顾名思义就是存储器芯片提供两个端口给两个CPU进行访问。

两个端口对同一主存操作有以下4种情况:

- 1.两个端口不同时对同一地址单元存取数据。成功。

- 2.两个端口同时对同一地址单元读出数据。成功。

- 3.两个端口同时对同一地址单元写入数据。写入错误。

- 4.两个端口同时对局一地址单完,二个写入数据,另一不读出数据。读出错误。

解决办法:

置“忙”信号为0,由判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间段后再访问。

3.习题常用

1.四体交叉存储器地址冲突

当给定的访存地址在相邻的四次访问中出现在同一个bank内,就会发生防存冲突。

例:某计算机使用4 体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的 地址对是 (D)。

-

8004 和 8008

-

8002 和 8007

-

8001 和 8008

-

8000 和 8004

四个模4同余的bank中,只有8000和8004在同一bank内且在一次连续的四次访问内。

2. 流水线示意图

若机器采用四体低位交叉存储器,现分别执行下述操作:第一(读取6个连续地址单元中存放的存储字,重复80次);第二(读取8个连续地址单元中存放的存储字,重复60次)则第一种、第二种所花费的时间之比为(C)

A.1:1 B. 2:1 C.4:3 D.3:4

绘制时间图如下

1:由于采用的是四体低位交叉存储器,所以在第一轮读取连续6个地址单元的时候,花费6×T4𝑇4时间,但开始第二轮的时候,由于M1模块还在占用中,需要再经历T2𝑇2时间,才能进行下一轮新的读取(再次进入下一轮的时候不需要第6个字读取结束,第5个读取结束,M1就空出来了,即可马上进入下一轮),中间的每一轮都不需要等待,最后一轮后读取完第二个M2后,还有半个T2𝑇2时间,所以答案是(80-1)×2T(前79轮按周期来算)+最后一轮的2T+最后一轮M2剩余的T2等于(80-1)×2T+2.25T=160.25T

2:每轮读取8个存储字刚好经过2T时间,每轮结束后,最近访问的M1刚好经过了时间T,此时可以立即开始下一轮的读取。前59次可以按照周期2T来算,最后一次为周期2T加上红色的三块时间(M4剩余的存储周期),所以答案是(69-1)×2T+(2T+0.75T)=120.75T

3. 低位交叉编址问题

某计算机主存按字节编址,由 4 个 64M×8 位的 DRAM 芯片采用交叉编址方式构成,并与宽度为 32 位的存 储器总线相连,主存每次最多读写 32 位数据。若 double 型变量 x 的主存地址为 804 001AH,则读取 x 需要的存储周期数是

A.1

B.2

C.3 (正确答案)

D.4

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)