Virtuoso使用layout绘制版图、使用Calibre验证DRC/LVS/PEX、ADE后仿真

Cadence Virtuoso版图绘制,Calibre使用(DRC/LVS/PEX),ADE前/后仿真

1 绘制版图

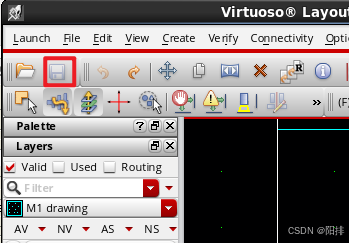

1.1 进入Layout XL

绘制好Schmatic后,在原理图界面点击Launch,点击Layout XL进入版图绘制界面。

1.2 导入元件

1、在Layout XL界面左下角找到Generate All from Source。

2、在Generate Layout界面,选中“Instance”,另外两个选项“I/0 Pins”和“PR Boundary”可以不选,点击OK。

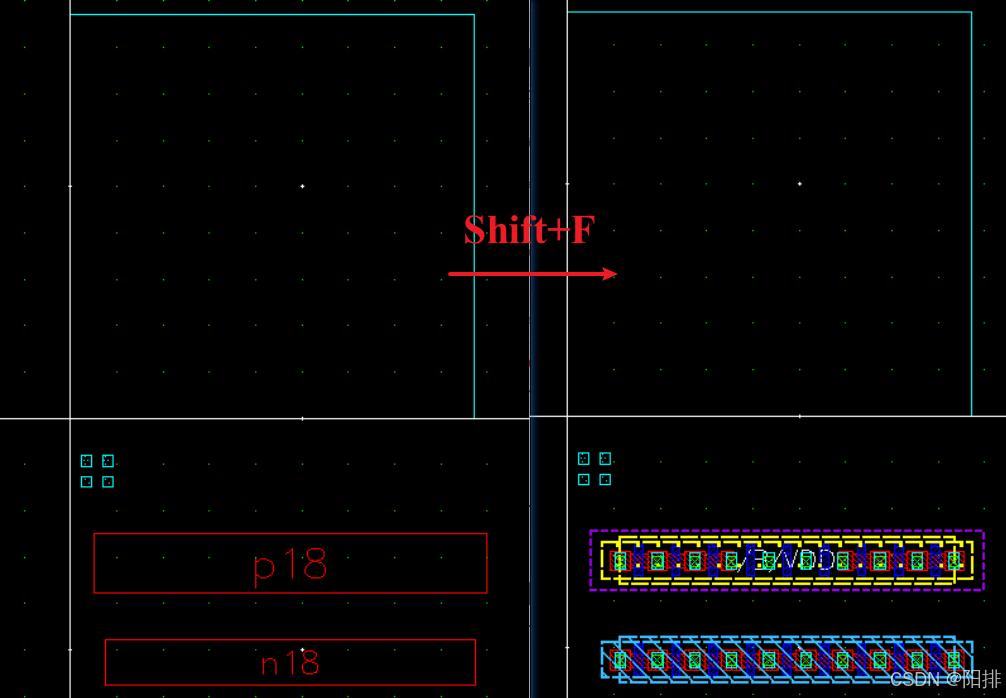

3、可以看到版图界面出现了元件边框,输入“Shift+F”显示元件所有层。

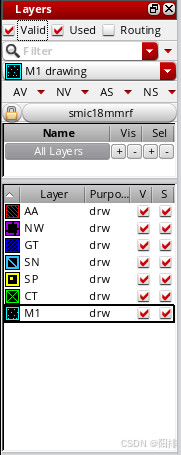

4、软件左侧为不同层,具体根据PDK手册进行区分。

顶部Valid、Used、Routing可以选择显示不同级别的层,一般点击Used就够用了。

1.3 绘制版图

这里不详细描述。

- 左侧打开原理图界面,右侧打开版图界面,可以进行交叉选择,即选择原理图内的元件或导线,版图界面的元件或导线会高光显示。

- 快捷键A为对齐操作,先点击要移动的元件,再点击参考元件。

- 快捷键P为布线,会自动吸附,如果要绘制某一层,可以先选择界面左侧的图层。

- 快捷键Q:先点击某个元件(一般为MOS管),然后按下Q,可以弹出元件属性,在Parameter中可以设置栅极、源极、漏极的连接方式。

- 快捷键O:过孔(Via),连接不同层。(PMOS、NMOS的基极都需要使用过孔连接到POWER或GND,具体情况具体分析,一般是过孔和N阱区/元器件边缘对齐)

- 一般需要将引脚通过过孔连接到顶层金属层,点击O后选择Stack就可以做一个直达的过孔,而不需要一层层叠起来。

- 快捷键L:标签,一般需要单独的层放置,直接叠在引脚上面,与引脚不接触的话可能LVS通过不了。

- 快捷键K:测量两个点之间的距离。

- Shift+G:添加Guard Ring,或者菜单栏点击Create->MPP Guard Ring。

- 旋转、镜像操作的图标如下:

- 对齐操作的图标如下:

- 如果找不到:可以在Window->Toolbars内部寻找。

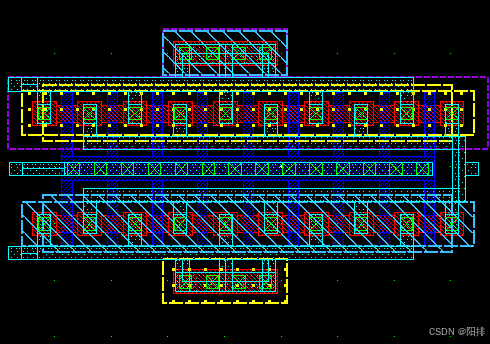

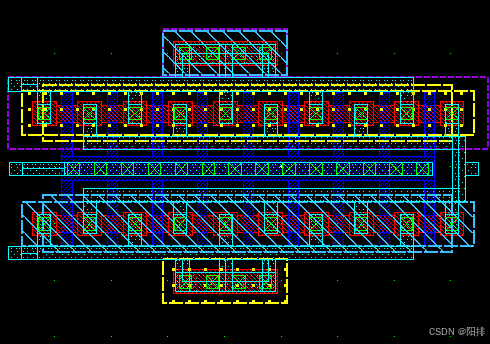

本人绘制的反相器版图如下:

1.4 保存

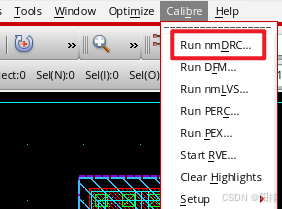

2 Calibre DRC

1、点击Calibre->Run nmDRC。

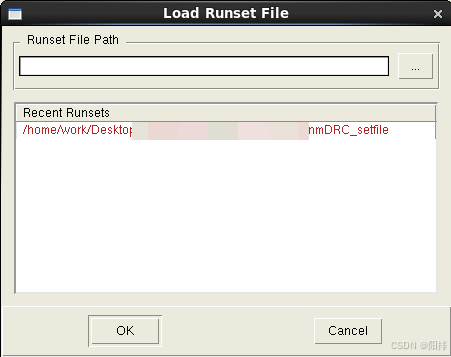

2、第一次跑DRC一般没有Runset,设置好DRC参数后保存,这里就能用了。这里可以直接Cancel。

3、导入DRC规则文件:

DRC Rules File一般会放在PDK包的Calibre/DRC内,选择.drc文件。

DRC Run Directory需要新建一个文件夹,否则生成的许多小文件会填满你的文件夹,非常杂乱。

4、点击Run DRC,运行。

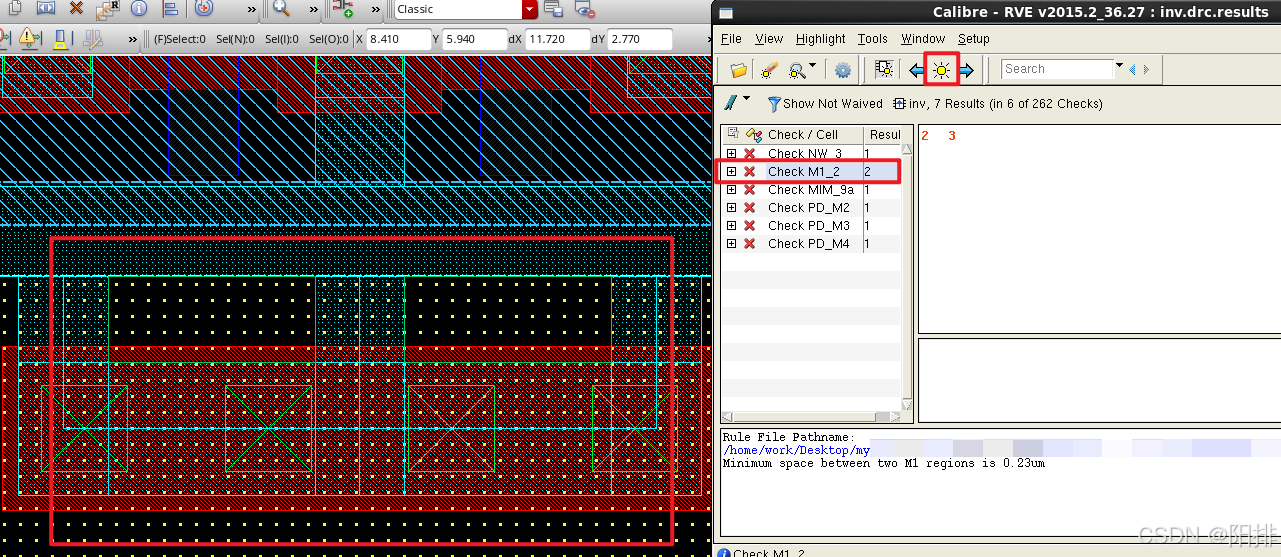

5、运行结束,查看result。

点击漏斗,Show Not Waived,查看设计规则违例的问题。

6、查找位置:选中一个违例,在界面下方可以查看违例原因;点击小太阳,即可在版图中查看违例位置。

一般来说,设计规则会有一个更详细的用户手册,设计师能在手册里看到图像化的设计规则。

找到违例后在版图中修改保存,然后继续运行DRC,不断消除错误。

如果是Density(密度)问题,查看问题报告和设计手册,可以添加Dummy管填充区域。

7、保存DRC Runset。

3 Calibre LVS

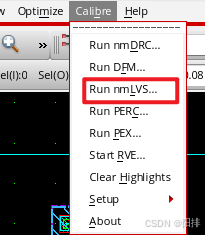

1、在Layout界面,点击Calibre->Run nmLVS。

2、Rules添加LVS规则文件:

LVS Rules File一般在PDK库内,选择.lvs文件。

另外设置一个LVS Run Directory。

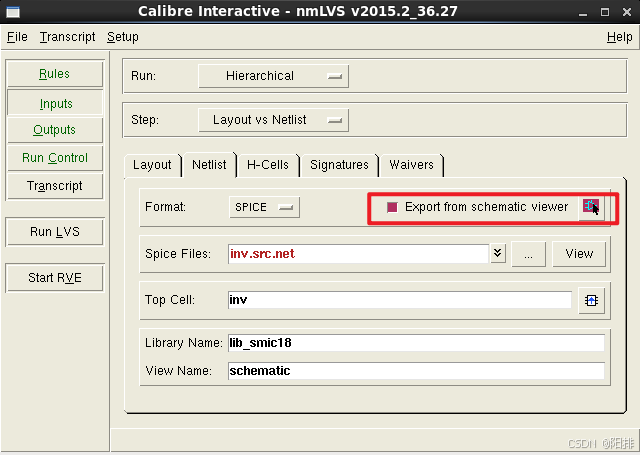

3、Input->Netlist中选择Export from schematic viewer,自动导入原理图中的网表。

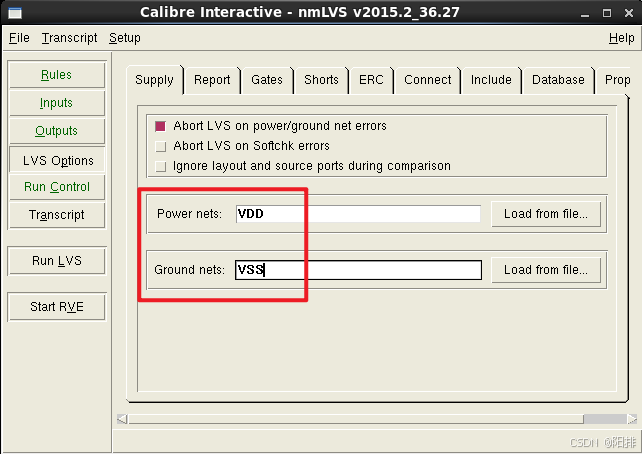

4、进入LVS Options:

手动输入自己的电源网络和地网络。

5、运行:Run LVS。

如果在1.3绘制版图部分没有设置Label或Label没放置在引脚上(Label的十字准星与引脚无接触),一般会输出错误。

需要查看.lvs文件,寻找Text、TXT、Label所代表的层,一般不能用在drawing层,会有一个单独的层放置Label(我的是M6TXT)。

也有可能Label的属性Connectivity中Net Name没有设置。

6、输出结果:

输出CORRECT的话,LVS通过;输出INCORRECT的话,仔细查看report,内部有错误信息。

7、保存LVS Runset。

4 Calibre PEX

使用PEX抽取RC之前需要进行LVS。

1、点击Calibre->Run PEX…

2、Rules添加.lvs的规则文件(跟上一节相同),不同的PDK设置可能不同,请自行查找对应解决方案。

#DEFINE RC_EXTRACT TRUE

#DEFINE RC_EXTRACT_FLOW XRC

#IFDEF RC_EXTRACT_FLOW XRC

include <rulefile_path>/rules.S //不同工艺角RC的规则,部分会有加密文件

include <rulefile_path>/rules.C //电容的规则

include <rulefile_path>/rules.R //电阻的规则

#ENDIF

- 部分较老版本的Calibre可能会无法解密文件,如果出现“Unable to initialize the decryption system”的问题,可以换一个Calibre试试。

Rules下设置PEX Run Directory到不同的目录下。

3、Inputs中Layout和Netlist都要选择“Export from layout/schematic viewer”。

部分PDK的H-Cells也要选择对应的LVS H-Cells file和导入PEX X-Cells file,一般会在rulefile相同的文件夹下。

4、Outputs

选择抽取模式为“xRC”,抽取等级为“Gate Level”,电阻电容为“R+C+CC”或者“RCC”(不同版本显示不同),电感可以设置为“No Inductance”。

PEX Netlist设置:

以下提供本人尝试的两种方法(第一种设置存在问题,第二种能成功导出电阻电容)

4.1 分支方法1(?)

5、Netlist Format设置为:“Spectre”或“Hspice”,这里设置类型取决于你用什么仿真器仿真。

Use Names From可以设置为“Layout Names”。

选择“Generate Calibre Connectivity Interface data”。

6、Run PEX。如果没有错误的话,进入下一步。

7、Start RVE。

运行没问题的话,点击Tools->Export CalibreView…导出数据。

在弹出的界面“Export Calibre View”,点击OK。

8、在“Calibre View Setup”上设置一下,点击“OK”。(图内设置可能存在问题)

然后会弹出“Calibre Info”。

此时在“Library Manager”相关Cell中查看View就可以看到添加的Calibre视图。

4.2 分支方法2(√)

5、PEX设置:

(1)Rules设置:rules选择PDK中的.lvs或者.rcx。

(2)Inputs设置:layout和netlist都要Export from *** viewer。

(3)Outpus设置:

- Extraction Type建议选择Transistor Level,R+C,No Inductance

- Netlist Format设置为:“CalibreView”。

- Use Names From设置为“Schematic”。

(4)PEX Options设置[6]:

在Include界面中添加Rule命令:

SOURCE CASE YES

LAYOUT CASE YES

6、点击Run PEX。一般会弹出.pex.netlist的RC网表和CalibreView设置界面。

7、设置Calibre View Setup。

- CalibreView Setup File可以不填。

- CalibreView Netlist File找到刚才生成的网表所在位置。

- Cellmap File一般为晶圆厂提供的PDK中TechFiles内部的文件。

- Calibre View Type选择Schematic。

- Create Terminals选择Create All Terminals [6]。

- Open Calibre CellView可以选择Read-mode,这样能打开查看。

- Generate SPECTRE Netlist可以勾选,会自动打开当前Cell的ADE L仿真界面。

点击OK后会弹出calibre视图和Calibre Info。

回到Library Manager界面上能看到calibre视图,点击即可进入寄生参数元件界面。

5 后仿真

如果4.2勾选了Generate SPECTRE Netlist,那么会直接弹出ADE L;没勾选的可以手动打开。

- 设置环境:点击Setup->Environment。

在Switch View List的开头添加calibre。

- 设置好参数后进行仿真:

(1)未调用寄生参数的仿真结果:

(2)调用calibre的仿真结果:

虽然波形不太对,但至少流程能跑完,以后再慢慢调整。

(3)修正:

- 错误原因:在inv的schematic内添加了analogLib的vdd和gnd,全局变量会影响仿真输出的值。

- 修改方法:删除原理图中除了PDK的其他库元件,只保留引脚,在最顶层引用的时候再调用analogLib库。

以下为不容易仿真出错的原理图绘制方法和调用方法。

修改后,调用calibre的仿真结果:

6 问题集锦

以下记录本人使用虚拟机运行Virtuoso碰到的问题。

6.1 无法使用ADE仿真

运行ADE仿真时遇到如下错误:

ERROR (ADE-3023): Cannot run simulations because the spectre executable is not found in the specified 'UNIX $PATH' setting.

Perform the following steps to specify the simulator executable path:

1.Download and install the required tool version from http://downloads.cadence.com:

- For analog simulations, download and install MMSIM

- For AMS simulations, download and install INCISIVE

2.After the installation is complete, set the tool installation path in your $PATH as below:

set path= $<MMSIM_INSTALLATION_PATH>/bin/<INCISIVE_INSTALLATION_PATH>/tools/bin:

$<IC_INSTALLATION_PATH>/tools/binpath

一般原因是MMSIM安装位置没有加入环境变量或者没有安装MMSIM。

解决方法为在网上找MMSIM的安装包、然后添加环境变量。

.bashrc配置一般较为不同,可以参考如下代码:

export MMSIM_HOME=/usr/Cadence/MMSIM151

export PATH=$PATH:$MMSIM_HOME/bin:$MMSIM_HOME/tools/spectre/bin

6.2 后仿真错误

错误记录:

ERROR (OSSHNL-912): Netlisting failed because terminal 'In2' specified in placed master 'lixiaoweiopperloop_second_order/symbol'

does not exist in switch master 'lixiaoweiopperloop_second_order/calibre'. To continue netlisting, either set the 'simCheckTermMismatchAction' to 'ignore', or set the

'simCheckTermMismatchAction' to 'warning' and 'nlAction' to 'ignore' for the missing terminal.

PEX设置问题,具体操作参考[6]。

7 参考资料与文档

部分patch、license和bashrc参考如下:

链接:https://pan.baidu.com/s/1sHQ3H1WiIB-TBijhACo7dw?pwd=v0d3 提取码:v0d3

参考文章如下:

[1] https://blog.csdn.net/weiwei_xiaoyu/article/details/130798333

[2] https://blog.csdn.net/qq_24941989/article/details/134758825

[3] https://zhuanlan.zhihu.com/p/343288844

[4] https://blog.csdn.net/Carol0630/article/details/124701320

[5] https://blog.csdn.net/bupt_qwLi/article/details/138328091

[6] https://bbs.eetop.cn/thread-876397-2-1.html

还有较多文档没放入…感谢各位网友的付出与交流!salute!

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)