【AD24报错】运行DRC后出现 Un-Routed Net Constraint ### Net Not Assigned 的解决方案

AD24在运行PCB设计规则检查(DRC)后报错:Un-Routed Net Constraint: Split Plane (No Net) on Power Dead Copper - Net Not Assigned.

·

AD24在运行PCB设计规则检查(DRC)后报错 Un-Routed Net Constraint ### Net Not Assigned 的解决方案

Un-Routed Net Constraint ### Net Not Assigned 的解决方案)

一、解决方案

仅记录本次报错的解决方案,请对照您的设计进行检查,如果是相同的设计问题,很高兴帮助您消除了一个报错。

在运行DRC之后系统报错:

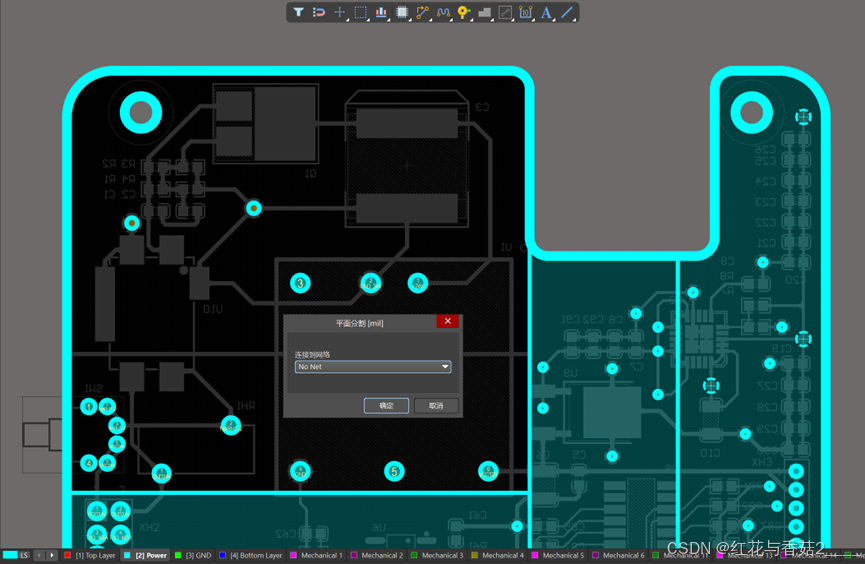

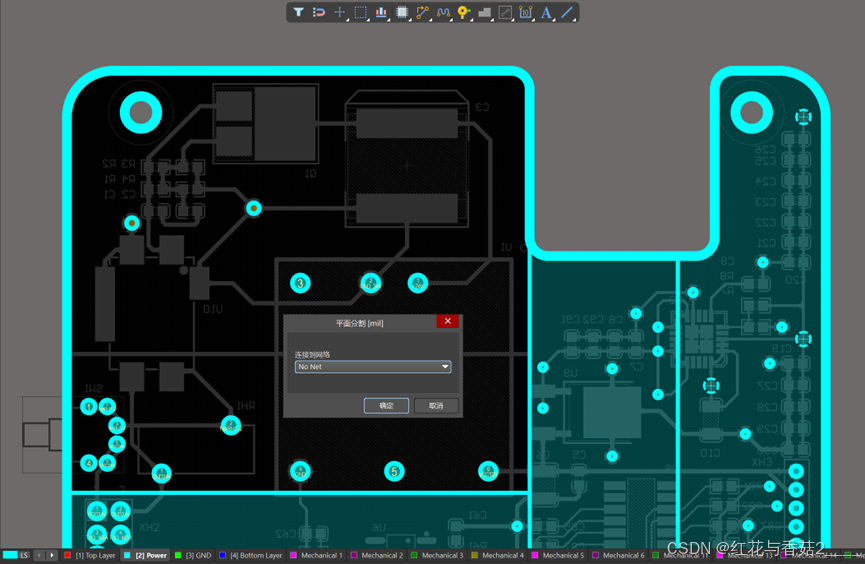

Un-Routed Net Constraint: Split Plane (No Net) on Power Dead Copper - Net Not Assigned.

翻译:非路由网络约束:电源死铜上的分割平面(无网络)-未分配网络。

在我的工程中,在负片层的设计找到有一块死铜,未分配网络。

将这块铜分配相应的网络。重新运行DRC。

清爽的Total 0,已解决。

二、可能会报错Dead Copper的因素

在 AD24 进行 PCB 设计规则检查后报 “Dead Copper” 错误,可能有以下方面的原因:

- 未连接的孤立铜箔:在绘制 PCB 时,可能不小心放置了一些没有与任何电路元件、走线或网络连接的铜箔区域。例如,在手动布线或调整布局时,残留了一些未正确连接的铜箔碎片。

- 网络连接丢失:原本应该连接到特定网络的铜箔,由于设计中的误操作或其他原因,与该网络的连接断开,从而形成了死铜。比如在移动元件或修改布线时,可能不小心破坏了铜箔与网络的连接。

- 敷铜参数设置问题:在进行敷铜操作时,相关参数设置不正确可能导致死铜的出现。例如,设置的 “去除死铜” 选项被勾选,而实际上一些看似孤立的铜箔可能在设计意图上是有连接的,但由于该选项的设置,被软件误判为死铜。另外,敷铜的连接方式、连接阈值等参数设置不合理,也可能导致部分铜箔无法正确连接到网络,形成死铜。

- 敷铜边界不完整:如果敷铜的边界没有正确定义或绘制不完整,可能会导致部分铜箔区域与主敷铜区域隔离,形成死铜。例如,在绘制不规则形状的敷铜区域时,边界的某些部分没有封闭,使得内部的一些铜箔无法与外部的铜箔连接。

- 层间连接问题:在多层板设计中,不同层之间的连接通过过孔等方式实现。如果过孔的设置不正确、数量不足或位置不合理,可能导致某些铜箔区域在层间无法正确连接,从而形成死铜。例如,过孔与铜箔的连接不良,或者过孔的网络属性设置错误,使得铜箔无法通过过孔与其他层的网络连接。

- 层的可见性和显示问题:有时候,由于层的可见性设置不当,一些死铜区域可能被隐藏或不易被发现。在进行设计规则检查时,这些隐藏的死铜区域可能会导致报错。例如,某些层的显示被关闭,而死铜恰好位于这些层上,导致在检查时无法正确识别其连接状态。

- 线宽和间距规则:如果设计规则中对铜箔的线宽、间距等有严格要求,而某些铜箔区域的尺寸或位置不符合这些规则,可能会被软件判定为死铜。例如,铜箔与其他元件或走线之间的间距过小,或者铜箔的线宽不符合设计要求,导致其无法正确连接到网络。

- 网络规则冲突:不同网络之间的连接规则可能会导致死铜的出现。例如,某些网络之间不允许有连接,但由于设计中的错误,一些铜箔跨越了不同的网络,从而被软件识别为死铜。

- 软件本身的问题或异常:AD24 软件本身可能存在一些错误或漏洞,导致在设计规则检查时误报死铜错误。这种情况相对较少,但也有可能发生。例如,软件在识别铜箔的连接状态时出现错误,将正常的铜箔区域判断为死铜。PCB 设计文件可能由于存储介质故障、软件异常退出等原因而损坏或丢失部分数据,这可能导致死铜错误的出现。例如,文件中的网络连接信息丢失,使得软件无法正确识别铜箔的连接情况。

三、可能会报错Un-Routed Net Constraint的因素

在使用 AD24(Altium Designer 24)进行 PCB 设计规则检查后出现 “Un-Routed Net Constraint” 报错,可能有以下几个方面的原因:

- 遗漏布线:在设计复杂的 PCB 时,可能由于疏忽或连接关系不清晰,导致某些网络没有进行布线。例如,在连接多个集成电路芯片时,可能遗漏了一些信号引脚的布线。检查原理图中的所有连接,确保每个网络都在 PCB 上有对应的布线。可以使用 AD24 的 “Navigator” 面板来查看未连接的网络。

- 布线中断:布线过程中可能出现意外中断,例如在调整布线时不小心断开了某条线路,或者由于设计规则冲突导致自动布线工具无法完成某些部分的布线。仔细检查 PCB 上的布线,特别是在密集区域和复杂的信号路径上,查找可能的中断点。可以使用 AD24 的 “Interactive Routing” 工具来手动修复中断的布线。

- 设计规则冲突:如果设计规则中对某些网络的线宽有严格要求,而实际布线的线宽不符合规则,可能会导致该网络被标记为未布线。例如,对于高电流的电源网络,可能需要较宽的线宽来承载电流,如果实际布线线宽不足,就会触发报错。检查设计规则中的线宽设置,并确保布线符合这些规则。可以使用 AD24 的 “Design Rules” 对话框来调整线宽规则,并重新进行布线。设计规则中的间距要求也可能导致布线问题。如果不同网络之间的间距过小,或者与其他元件或障碍物的间距不符合规则,可能会影响布线的完整性。检查设计规则中的间距设置,并确保布线满足这些要求。可以使用 AD24 的 “Board Inspector” 工具来查看和调整元件之间的间距。

- 元件封装问题:元件封装的引脚定义可能与原理图中的元件不一致,导致布线无法正确连接。例如,封装的引脚编号或方向错误,会使布线无法连接到正确的引脚。检查元件封装的正确性,确保与原理图中的元件对应。可以使用 AD24 的 “Library” 面板来查看和编辑元件封装。元件封装的尺寸可能与实际元件不匹配,导致布线困难或无法连接。例如,封装过大或过小,可能会影响周围元件的布局和布线。选择合适的元件封装,并确保其尺寸与实际元件相符。可以参考元件的数据手册和封装库中的信息来选择正确的封装。

最后,欢迎交流学习。

解决方案与项目截图为作者原创,转载请标明出处。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)