什么是隔离芯片?一文看懂隔离芯片的分类和产品矩阵

根据实现原理不同,隔离器件可以分为光电耦合隔离器(简称“光耦”)和数字隔离芯片两种,其中数字隔离基于 CMOS 工艺为电子系统中数字和模拟信号的传递提供电阻隔离特性,根据耦合元件不同又分为磁感耦合隔离芯片(简称“磁耦”)、电容耦合隔离芯片(简称“容耦”)和巨磁阻隔离等类型,因巨磁阻隔离应用相对较少,下文主要讨论光耦、磁耦与容耦。在隔离系统中隔离两端由于经常发生高压共模信号跳变,可能造成隔离器件的信

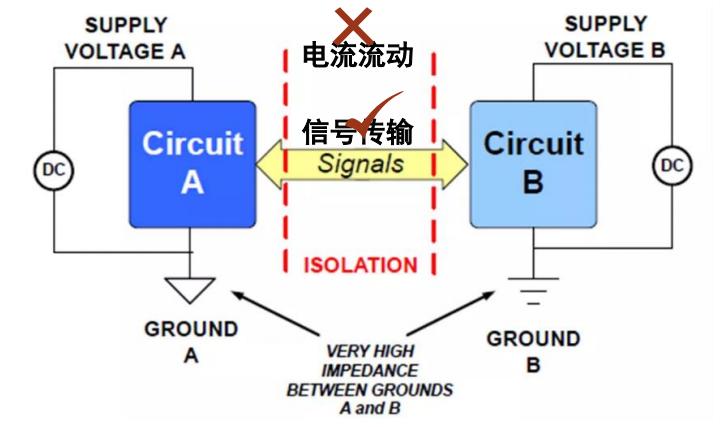

隔离芯片是保障电路安全的模拟芯片。隔离芯片属于模拟芯片,是信号链领域的细分产品门类,在电气隔离状态下实现信号的耦合传输。如下图所示,数据信号可以在 AB 两个区域之间进行传输,同时避免电流在 AB 两个区域之间流通,确保没有实际的电气连接。在工业、通信、新能源等复杂应用场景下,一个综合的电子系统有众多不同电压等级的子系统,各子系统数据传输时会产生串扰,且高电压也会导致电路安全问题,因此需要通过隔离芯片来实现电气隔离并保证信号传输的准确、稳定、可靠。具体来说,隔离芯片在电子系统里可实现三类功能:

1)安全防护:提升高压电路的安全性,保护电子控制设备和操作人员安全;

2)信息传输:在具有相对较高的电位差的子电路系统之间进行有效通信,即保障强电电路和弱电电路之间信号传输的安全性;

3)抗干扰:去除两个电路之间的接地环路,阻断共模、浪涌等干扰信号的传播,防止电气噪声破坏敏感信号,从提升电磁兼容性。

图 1:隔离芯片所处电路位置

图2:隔离芯片可以通过消除接地环路来降低噪声/EMI(抗干扰性)

图 3:隔离芯片在高压电路下可提供安全防护

隔离芯片广泛应用于电动车、工业等中高压场景,在客户端属于与安全相关的重要料号,安规认证是关键。

一般来说,涉及到高电压(强电)和低电压(弱电)之间信号传输,或者AC-DC 或中高电压 DC-DC 电源转换的设备大都需要进行电气隔离并通过安规认证,因此隔离芯片广泛应用于信息通讯、电力电表、工业控制、新能源汽车等各个领域。

此外,由于隔离芯片是保障电路安全的关键芯片,下游客户采购隔离芯片时对其可靠性的重视程度较高:业内对数字隔离类芯片存在相关的产品认证制度,不同领域所需的安规认证种类较多,进行安规认证时对产品性能要求高且认证时间较长,取得全球各国、各行业、各目标市场所认可的安规认证已成为隔离芯片行业主要壁垒之一。因此在电动车、工业等客户领域,模拟芯片厂商可以将隔离芯片作为切入中高端应用场景的“突破口”,强化客户粘性和认可,有助于继续导入其他模拟芯片,打开后续成长空间。

图 4:隔离芯片在半导体产业链所处位置

隔离芯片性能评价指标包括传输速率&时延、CMTI、ESD 防护等。作为一种安规器件,隔离芯片主要在通讯、工业、汽车等场景下的高压环境中工作,其性能指标主要体现其在恶劣的环境下的稳定性。目前业内评价隔离芯片产品的通用指标包括:

1)信号传输速率&时延:传输速率代表数字隔离器能够准确传输的信号速率、传输时延代表信号输入到输出的时间;

2)CMTI(共模瞬态抗干扰能力):在隔离系统中隔离两端由于经常发生高压共模信号跳变,可能造成隔离器件的信号传输误码,CMTI 将直接影响系统的稳定性,因此是衡量隔离性能的核心指标之一;

3)ESD 防护:由于静电会对电子系统造成严重危害,可以在不经意间将电子器件击穿,而隔离器件往往处于系统的接口处或导电的关键路径,因此 ESD 防护(静电防护)能力也成为衡量隔离性能的核心指标之一;

4)隔离耐压:是美国 UL 安全试验(美国最权威的安全试验和鉴定的机构)所进行安规试验的主要认证项目之一,该指标是对隔离器件的整体耐压性能的衡量;

5)浪涌抗扰度:由于在电力系统开关瞬间或雷击发生的瞬间产生的电压将远远超过工作电压,需要有隔离器件抵御高电压传输时产生的浪涌,因此浪涌抗扰度也是核心指标之一。

表 1:隔离芯片产品性能行业通用评价指标

技术路线

光耦/磁耦/容耦三种技术并存,容耦占比逐步提升

隔离芯片目前已形成光耦隔离、磁耦隔离、容耦隔离三种技术路径。根据生产工艺、电气结构和信号传输原理不同,隔离可以通过光学、电感或电容耦合技术实现。根据实现原理不同,隔离器件可以分为光电耦合隔离器(简称“光耦”)和数字隔离芯片两种,其中数字隔离基于 CMOS 工艺为电子系统中数字和模拟信号的传递提供电阻隔离特性,根据耦合元件不同又分为磁感耦合隔离芯片(简称“磁耦”)、电容耦合隔离芯片(简称“容耦”)和巨磁阻隔离等类型,因巨磁阻隔离应用相对较少,下文主要讨论光耦、磁耦与容耦。

图5:三种隔离技术路线图示

图 6:容耦数字隔离芯片内部详细结构图

(红框部分为电容内部结构)

光耦:基于光电效应实现信号传输。

光耦的物理基础是光电效应:光耦隔离器是将发光器(基于 GaAs 的 LED 器件)与光接收器(光敏三极管)封装在同一管壳内,当输入端加电信号时发光器发出光线,光接收器接受光线之后就产生光电流,在运算放大器放大后从输出端流出,这就实现了“电—光—电”转换,从而实现了两个端口间的信息传输。

光耦是上世纪 70 年代发展起来的隔离器件,直至 1990 年代后期,光耦都是市场上唯一的解决方案,其代表厂商是安华高(已被博通收购)。

光耦的优点在于:

1)方案成熟并久经市场考验;

2)抗干扰能力强;

缺点:

1)一般数据传输速率较低,在高速场景下使用难度大;

2)功耗较高;

3)由于光衰问题的存在,器件的性能表现会随着使用时间增加而降低;

4)由于 LED 物理尺寸的限制,光耦隔离器的体积难以减小;

5)隔离等级相对受限。

磁耦:基于电磁感应定律实现信号传输。

磁耦的物理基础是电磁感应定律:磁耦数字隔离芯片内部结构包含变压器,当输入端的加电信号会引起电流变化,由于电磁感应定律,变压器线圈的另一端也会产生相应的电流变化生成电信号,从而完成两个端口间的信息传输。磁耦技术主要基于 CMOS 工艺,2007 年由 ADI 率先推出,其代表厂商包括ADI、英飞凌。

磁耦的优点在于:

1)传输速率高;

2)由于采用 CMOS 工艺,在集成度、功耗、体积等方面均优于光耦;

缺点:

1)易受外部磁场干扰,其辐射以及抗辐射性能相对较差;

2)生产时需在 CMOS 工艺基础上增加两道工序,成本相对较高。

容耦:通过电容两块极板之间的电场变化来实现信息传输。

容耦数字隔离芯片是基于 CMOS 工艺串联两颗电容器在一颗芯片,并通过高频信号调制解调(如 ook 调制技术)将输入信号通过电容隔离之后传输出去,即通过电容的两块极板之间电场变化来传递信息。容耦技术是 Silicon Labs 在 2009 年于业内首发,代表厂商包括 TI、Silicon Labs,国内纳芯微、川土微、荣湃等厂商均采用容耦技术路线。

容耦的优点包括:

1)抗干扰能力强:容耦绝缘层的填充材料是二氧化硅,具有很稳定的可靠性和耐用性以及抗磁干扰能力和抗瞬态电压能力,优于光耦和磁耦采用的聚酰亚胺材料;

2)同样采用 CMOS 工艺,在集成度、功耗、体积等方面均优于光耦;

3)与磁耦相比,容耦不需要晶圆的二次加工,其成本相对较低;缺点在于防静电能力需要专门进行优化。

目前数字隔离替代光耦的趋势明确,其中容耦技术逐步成为主流发展方向。与传统的光耦相比,数字隔离芯片基于 CMOS 工艺,是更新一代、尺寸更小、速度更快、功耗更低、温度范围更广的隔离器件,并且拥有更高的可靠性和更长的寿命,是目前产业发展方向,目前正逐步替代光耦。在数字隔离器的几种方案中,容耦在抗干扰、成本等方面优于磁耦,在下游市场端渗透更快,目前国内新进入者也纷纷选择容耦作为主要发展方向。

表 2:三种隔离技术对比

产品矩阵

以数字隔离器为基础,构建丰富产品矩阵

隔离芯片包括标准数字隔离器、隔离接口、隔离驱动、隔离采样、隔离电源五大品类。标准数字隔离器是隔离芯片产品最简单的产品形态,只负责实现电气隔离与信号传输,而将标准数字隔离器与不同模拟芯片集成的方式可以进一步丰富隔离芯片的产品形态并拓展其应用场景,目前已形成隔离接口、隔离驱动、隔离采样、隔离电源等丰富的“隔离+”产品矩阵,其中:

隔离接口:隔离+接口芯片

接口芯片是基于通用和特定协议且具有通信功能的芯片,广泛应用于电子系统之间的信号传输,可提高系统性能和可靠性。常用接口按照协议可划分为 I2C、CAN、LIN、RS-485、RS-232 等系列,其中 I2C、CAN、LIN 在车载电子中应用广泛。将接口芯片与标准数字隔离器集成为隔离接口芯片产品,能够在具备通信功能的同时实现电气隔离,从而提升接口芯片产品的安全保障。

隔离驱动:隔离+栅极驱动芯片

栅极驱动芯片是驱动 IC 的一个细分品类,主要用来驱动 MOSFET、IGBT、SiC、GaN 等功率器件的芯片,能够放大控制芯片(MCU)的逻辑信号,包括放大电压幅度、增强电流输出能力,以实现快速开启和关断功率器件。将栅极驱动与标准数字隔离器集成为隔离驱动芯片产品,能够在驱动功率器件的同时,提供原副边电气隔离功能;此外,相较于非隔离驱动在耐压能力方面的局限性(工作电压不超过 700V),隔离驱动可以更好地满足高耐压需求,承受 10kV 以上的浪涌电压,已成为高功率应用中的首选。此外,隔离驱动开发需适配功率器件厂商,因而开发难度较高。

隔离采样:隔离+运放/ADC

隔离采样包括各类隔离运算放大器和隔离 ADC,可在实现电气隔离的同时,完成对电压/电流等信号的采样或模数转换。

隔离电源:隔离+电源管理芯片

隔离电源是电源的输入回路和输出回路之间没有直接的电气连接,输入和输出之间是绝缘的高阻态,没电流回路。隔离电源能够实现作业人员安全,使各模块供电独立、可靠及稳定。

图 7:隔离+芯片产品梳理

了解更多隔离芯片资讯,请访问芯智雲城:

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)