【深入浅出 FPGA】同步复位、异步复位以及异步复位同步释放

异步复位同步释放在复位信号到来时不受时钟信号的同步,而复位信号释放时受时钟信号的同步。为消除亚稳态,在复位信号释放时,利用两个统一时钟沿的层叠寄存器(打两拍),将复位信号同步化:同步复位只有在时钟触发沿来到是,复位信号才有效。复位信号超过一个时钟周期,才可保证复位成功;异步复位只要复位信号有效则系统立即复位,但复位信号释放时易产生亚稳态。

一、FPGA复位

- 复位的目的是什么?

通俗的讲复位的目的就是让寄存器、电路以及系统处于一个已知的初始状态。 - 未曾触碰复位按键,为何程序也能复位?

FPGA内部存在有上电复位功能的上电复位电路POR(Power On Reset)。FPGA有上电检测模块,一旦检测到电压超过检测门限后,即会产生上电复位脉冲传输至所有寄存器。

二、同步复位

同步复位只有在时钟触发沿来到时,复位信号才有效。

Verilog代码如下:

module Sync_rst(

input sys_clk ,

input sys_rst_n ,

input data_in ,

output reg data_out

);

always @(posedge sys_clk)begin

if(!sys_rst_n)

data_out <= 1'b0;

else

data_out <= data_in;

end

endmodule

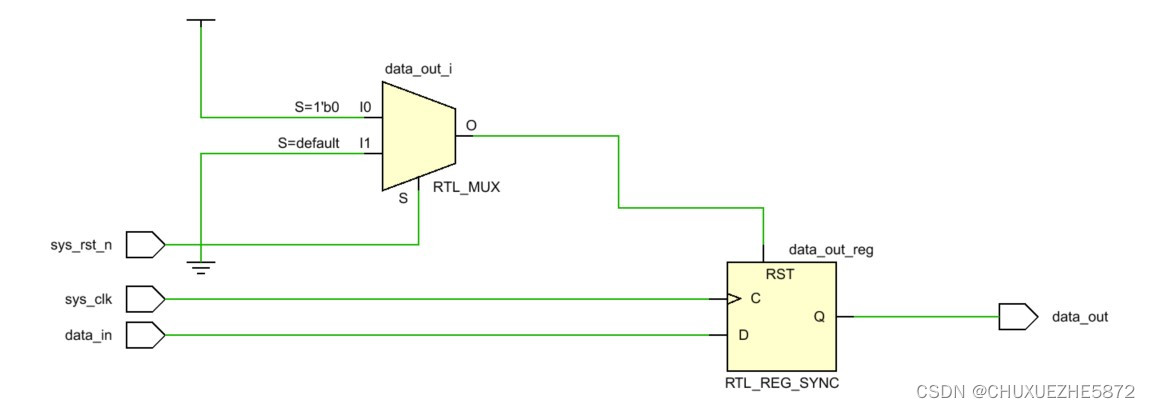

同步复位RTL视图:

同步复位仿真代码:

`timescale 1ns / 1ps //时钟单位/时钟精度

module tb_test(

);

reg sys_clk ;

reg sys_rst_n ;

reg data_in ;

wire data_out ;

//初始化测试条件

initial begin

sys_clk = 1'b0;

sys_rst_n <= 1'b1;

data_in <= 1'b1;

#20

sys_rst_n <= 1'b0;

#14

sys_rst_n <= 1'b1;

#57

sys_rst_n <= 1'b0;

#17

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk; //时钟周期为20ns

//实例化同步复位模块

Sync_rst u_Sync_rst(

.sys_clk(sys_clk) ,

.sys_rst_n(sys_rst_n) ,

.data_in(data_in) ,

.data_out(data_out)

);

endmodule

同步复位仿真结果:

红色方框内,因复位信号少于一个时钟周期且未在时钟上升沿有效,导致系统未检测到复位,故复位次复位信号无效。

同步复位优点:

- 电路稳定性强:能保证电路同步,复位只发生在有效沿。

- 益于去除毛刺:可剔除复位信号中短于时钟周期的毛刺。

同步复位缺点:

- 复位信号大于时钟周期:由于复位信号只发生在有效沿,则复位信号长度必须大于时钟周期才能保证复位成功。

- 逻辑资源消耗较多:大多数场商目标库内的触发器都只有异步复位端口,采用同步复位需消耗较多逻辑资源。

三、异步复位

只要复位信号有效则系统立即复位。

Verilog代码如下:

module Async_rst(

input sys_clk ,

input sys_rst_n ,

input data_in ,

output reg data_out

);

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

data_out <= 1'b0;

else

data_out <= data_in;

end

endmodule

异步复位RTL视图:

异步复位仿真初始化条件与同步复位相同。

异步复位仿真结果:

虽复位条件未超过一个时钟周期,但复位成功。

红色方框处易产生亚稳态。

同步复位优点:

- 消耗逻辑资源少:由于大多数的厂商目标库内的触发器都有异步复位端口(CLR),可以节约逻辑资源。

- 复位信号触发率高:由于采用复位信号下降沿触发,复位信号都可被触发。

同步复位缺点:

- 易受外界毛刺干扰:由于复位较为灵敏,无法滤除毛刺。

- 易产生亚稳态:由于复位信号释放是随机的,若释放处在时钟触发沿(不满足最小建立时间和最小保持时间),会产生亚稳态(不确定是0还是1)导致输出数据错误。

四、异步复位同步释放

该复位方式在复位信号到来时不受时钟信号的同步,而复位信号释放时受时钟信号的同步。为消除亚稳态,在复位信号释放时,利用两个统一时钟沿的层叠寄存器(打两拍),将复位信号同步化。

Verilog代码如下:

module rst(

input sys_clk ,

input sys_rst_n ,

input data_in ,

output reg data_out

);

reg sys_rst_n_reg0;

reg sys_rst_n_reg1;

//对复位信号打两拍

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

sys_rst_n_reg0 <= 1'b0;

sys_rst_n_reg1 <= 1'b0;

end

else begin

sys_rst_n_reg0 <= sys_rst_n;

sys_rst_n_reg1 <= sys_rst_n_reg0;

end

end

//使用同步后的复位信号对数据进行复位

always @(posedge sys_clk or negedge sys_rst_n_reg1)begin

if(!sys_rst_n_reg1)

data_out <= 1'b0;

else

data_out <= data_in;

end

endmodule

异步复位同步释放RTL视图:

异步复位同步释放仿真初始化条件与上述两种复位方式相同。

异步复位同步释放仿真结果:

异步复位同步释放优点:

- 电路稳定性强: 对复位信号进行同步后,该信号释放时,满足时钟的最小建立时间和最小保持时间,有效的去除了亚稳态。

- 响应速度快:有效捕获复位信号,复位信号短于一个时钟周期也能复位。

异步复位同步释放缺点:

- 相较于前面两种复位方式,该复位方式实现较为复杂。

五、小结

异步复位同步释放效果最为理想,但实际开发中一般采用异步复位。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)