SAR ADC关键技术 —— 采样开关

对于SAR ADC来说,电荷再重分配的SAR ADC因不消耗静态电流,功耗可以非常低,同时可兼顾采样和保持功能,故成为低功耗 SAR ADC中DAC的主要实现形式。这种结构SAR ADC的主要由采样保持电路、CDAC、比较器和 SAR 逻辑这四部分组成。采样保持电路是 SAR ADC 的第一级,后级的量化均基于保持阶段的电压,其性能限制了整个 ADC 的最高转换精度。

后面准备讲一下做最基本SAR ADC的一些关键技术,如采样保持电路、CDAC、比较器和 SAR 逻辑等,看的人多的话,后面几个就都介绍一下,先从第一个开始吧,这也是最简单的。

采样保持电路是 SAR ADC 的第一级,后级的量化均基于保持阶段的电压,其性能限制了整个 ADC 的最高转换精度。为实现信噪比的最大化,输入信号一般是全电压范围,采样电路需要完成实现轨到轨且高精度的信号采样的功能。SAR ADC 的采样实质是一个RC充电过程,其采样保持的电容可以复用 DAC电容阵列,采样保持电路的带宽由开关的电阻 Ron和采样段看到的总电容 Ctot确定。最传统的采样开关是单个 MOS 管或 CMOS 传输门,通常工作在线性区,可以等效为一个电阻。

其导通电阻可以推导如下,可见其导通电阻会随着输入电压的变化而变化,图2显示了了不同电压下三种开关导通电阻的变化。

由上式和图2可知,在采样阶段下,栅极接高电平(VDD),当输入电压增大并接近 VDD-Vth时,开关导通电阻剧增,时间常数增加,采样精度降低;当输入电压大于 VDD-Vth时,晶体管截止,采样电压无法跟随模拟输入信号波动。值得注意的是,不仅 VGS 会随着 Vin 变化,由于背栅效应的影响,阈值电压 Vth也随Vin变化,从而使得沟道电阻随电压发生非理想失真。

因此 CMOS 传输门开关的优势显现,其电路如图3所示,采样时不受栅压的限制,可以轨到轨进行采样跟随,对于较低速度和精度的 ADC 而言,可以使用CMOS 传输门作为采样开关。但是从图4可知,即使是传输门结构,采样开关的导通电阻也是与输入信号相关的,而且衬底调制效应仍然存在。对于高精度的 ADC 而言,这种采样开关导通电阻带来的非线性仍然是不可接受的,其次对于高速 ADC 而言,NMOS 和 PMOS 关断速度不一样可能会造成采样电压的失真。

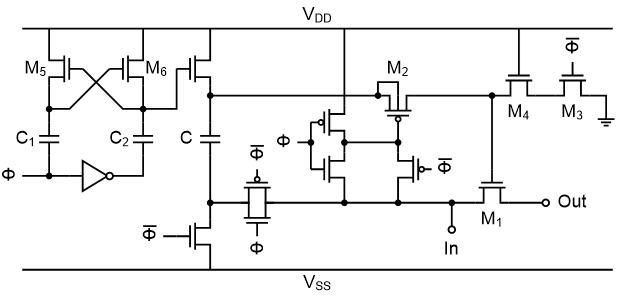

对于高精度的SAR ADC而言,采样开关常通过自举电路实现。自举是一种利用电容两端电压不瞬变的特性来实现信号电压抬升的技术,其核心是一个自举电容器。采样开关利用自举技术能将 NMOS 开关管的栅源维持恒定偏压,即把 NMOS 管的 VGS 固定成自举产生的直流量,VGS 与输入信号无关,进而消除了电阻调制效应,实现显著提升采样电路性能的效果,图4是一种典型的自举开关结构图。

栅压自举开关电路在 ϕ=0相位时,将电容一端接地,另一端接 VDD进行充电,同时将 NMOS 开关管栅极接地保持采样关断;在ϕ =1相位时将 Vin接电容下极板,同时将电容上极板接到 NMOS 开关管栅极,开启采样过程从而将 NMOS 开关管的栅压自举到 VDD+ Vin,保持采样开关导通时的过驱动电压恒定为 VDD,这时的导通电阻与输入电压无关。虽然 Bootstrap开关基本解决了导通电阻造成的非线性问题,但是依然有时钟馈通以及电荷注入等影响采样精度的因素存在。

沟道电荷注入:在采样阶段,栅极接高电平,开关导通,输出电压跟随输入信号变化,开关存在沟道导通电荷;在保持阶段,开关断开,电荷从源漏两端流出,靠近信号 Vin侧流出的电荷被 Vin 吸收,对输出信号没有影响;但靠近输出侧流出的电荷被采样电容 Cs 吸收,由于开关管与输入电压相接,此电荷注入与 Vin相关,导致非线性,从而引入了采样误差,如图 2 所示。

沟道电荷注入效应是所有上极板采样电路都面临的问题。为解决这一问题,一种常见的方式是增设另一相反动作的虚拟 MOS 管吸收注入的电荷,如果有一半的沟道电荷在截止时流入输出端,虚拟管栅尺寸设定为采样管的 50%可进行补偿,但在实际中由于沟道注入效应的复杂非线性,注入的电荷很难被完全吸收,无法从根本上消除这个误差。另一种比较有效的解决方式就是采用下极板采样。

时钟馈通:只考虑采样电容端的话,时钟馈通的主要来源为开关管栅极与输出端的寄生电容,如图6中的 Cp。在 NMOS 开关管栅极产生时钟跳变时,会通过寄生电容 Cp耦合到输出端的采样电容上,造成采样电荷的误差而影响采样电压。由

可知,时钟馈通效应造成的误差ΔV与输入信号幅度无关,因此最终体现为固定的失调电压。

关于采样开关的,先讲到这,后面会再提一下采样方式和开关切换方式。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)