FPGA远程固件在线升级

一般在代码开发阶段,我们使用JTAG烧写代码,但当产品投入到实际使用过程中,难以再用JTAG进行固件更新。所以需要开发远程/在线更新的功能,即使用产品自带的通讯接口(如串口,以太网接口等)传输待更新的固件包,实现固件更新升级的功能。

FPGA远程固件在线升级

1.摘要

对最近做的FPGA远程更新/在线升级做一个总结。一般在代码开发阶段,我们使用JTAG烧写代码,但当产品投入到实际使用过程中,难以再用JTAG进行固件更新。所以需要开发远程/在线更新的功能,即使用产品自带的通讯接口(如串口,以太网接口等)传输待更新的固件包,实现固件更新升级的功能。本文所使用的平台是ALTERA公司的cyclone IV E系列产品EP4CE30F23I7,PC通过串口将待更新的固件包传发送到FPGA,FPGA将接收的固件包写入FPGA的配置 flash:EPCS16中,并以新收到的固件包覆盖原来通过JTAG烧写的代码,当芯片重新上电或者进行一次重配置,FPGA便会执行新的固件包。

2.FPGA上电加载过程

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,FPGA才能正常运行。EP4CE30F23I7采用EPCS16作为配置芯片,所以我们要做的就是将要更新的固件包烧写到此EPCS16芯片中。每次芯片上电,配置电路就会加载EPCS16中的固件包,进行一次配置,FPGA还有一个重配置的ip核,也可以在FPGA运行过程中进行重配置。

FPGA上电后会自动从0地址开始加载镜像文件(把一个FPGA工程综合生成的文件成为一个镜像文件),看别人说的rpd文件末尾至少留32个字节的FF,我认为可能是加载到32个连续的FF就会停止加载文件。

我的思路是编写一个工程称为出厂配置工程,再编写一个工程称为应用工程,应用工程是我们正常的编写的工程,也就是我们需要更新的固件。将出厂配置工程转换成jic文件并通过JTAG烧进flash中,但是只将该文件烧写在flash的前几个扇区,具体几个扇区由你的出厂配置程序的大小来定,我自己生成的jic文件占用6个扇区,在生成Jic文件时可以选择代码在flash中的地址的,所以我的出厂配置所占的地址范围为0x0 ~ 0x5FFFF,占前6个扇区。而我编写的应用工程则放在从0x60000开始地址的地方,在线烧写镜像文件时,将需要更新的文件从0x60000地址开始写就可以了。我们在线烧写的是rpd文件,后面具体介绍这几种文件。

2.1FPGA配置方式

1.JTAG方式

通过JTAG接口,利用Quartus II软件可以直接对FPGA进行单独的硬件重新配置。Quartus II软件在编译时会自动生成用于JTAG配置的.sof文件。如果同时使用AS方式和JTAG方式来配置FPGA,JTAG配置方式拥有最高的优先级,此时AS方式将停止,而执行JTAG方式配置。

2.FPGA主动串行(AS)方式

主动串行配置方式(AS)是将配置数据事先存储在串行配置器件EPCS中,然后在系统上电时Cyclone IV FPGA通过串行接口读取配置数据(如果是压缩数据,还会进行解压缩处理)对内部的SRAM单元进行配置。因为上述配置过程中FPGA控制配置接口,因此通常称为主动配置方式。在配置期间,Cyclone IV用过串行接口来读配置数据,来对里面的SRAM编程。串行配置器件的四个接口包括,串行时钟输入DCLK,串行数据输出DATA,低有效的片选信号NCE,串行数据输入ASDI。本文就是采用这种方式。

3.FPGA被动(Passive)方式

此方法用的较少,不做介绍。

2.2配置芯片EPCS16

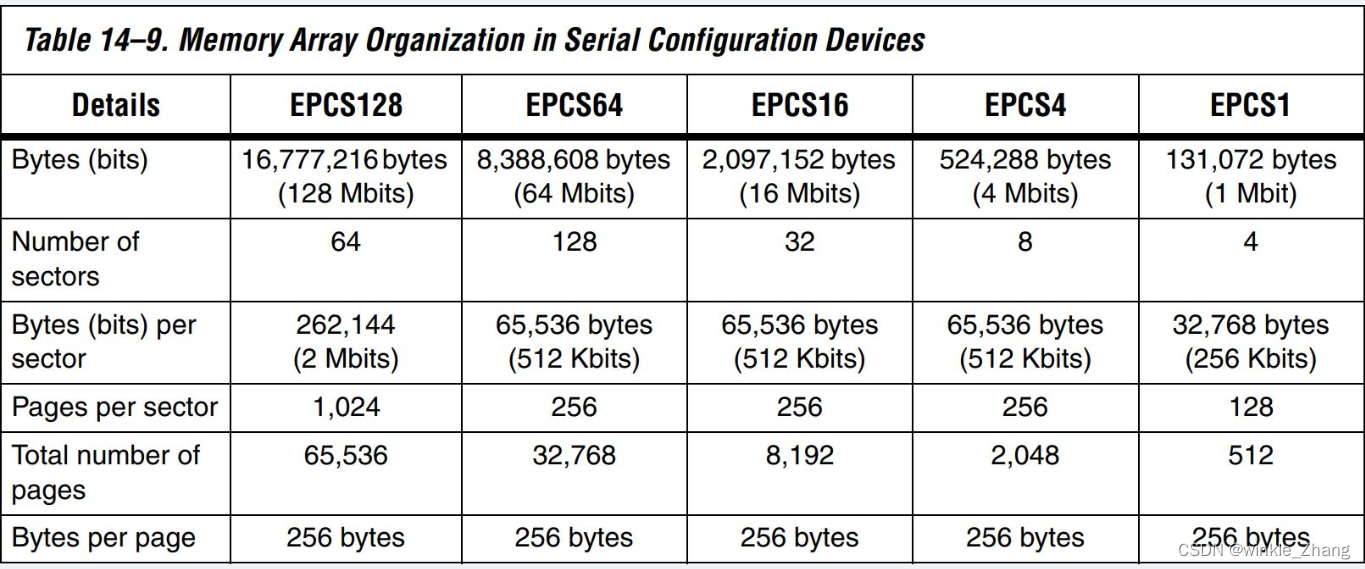

如上图为EPCS系列容量表。EP4CE30F23I7采用EPCS16作为配置芯片,EPCS16共有16Mbit的存储空间被分成了32个扇区( sector),每个扇区又分成256页( page),每一页包含256字节。EPCS16各扇区的字节地址如下图所示:

对EPCS16的具体操作,在讲到ASMI IP核时再具体讲,我们利用ALTERA官方的IP核来对EPCS16进行擦除、读、写的操作。

2.3FPGA生成的几种文件

1.sof文件

sof文件是编译(分析、综合、布线、生成、时序)过程中生成的一个文件,生成的sof文件是可以直接通过JTAG口下载到FPGA的SRAM中去并直接执行。

2.jic文件

jic文件不是在编译过程中生成的,而是需要使用Quartus II软件的“Convert Programing File”功能将sof文件转换得到的。得到的jic文件,通过JTAG口可以将jic文件通过FPGA作为桥接芯片下载到配置芯片中去。

3.pof文件

pof文件和sof文件一样也是在Assemble过程中生成的,但是pof文件是不能直接下载到FPGA的SRAM中去的,而是通过ASP端口直接下载到FPGA的配置芯片中去的。配置芯片一般是串行FLASH芯片,在上电的时候FPGA会主动的从配置芯片中读取数据并烧写内部的SRAM数据然后执行程序。(在assignments – device – device and pin option, 在configuration 选项卡当中,要勾上Use Configuration device,并选择好配置芯片。 选择configuration scheme为Active Serial,编译就能生成pof文件)

4.rpd文件

rpd文件为包含cyclone系列芯片二进制位流数据和配置数据的二进制文件的合成文件。我们生成rpd文件前,先要生成Pof文件再用Quartus II软件的“Convert Programing File”功能将pof文件转换成rpd文件。

我们一般是通过JTAG将Jic文件烧进EPCS16,在线升级是将rpd文件通过串口/网口等方式烧进EPCS16,当然烧写的过程是依靠FPGA来完成,我们要写一段代码用来接收串口/网口数据,将其写入EPCS16中。jic、rpd文件生成时,都是占2M字节,但文件内实际有效的并没有那么大,其中无效的数据都由FF填满,可以手动删除,但至少保留32个字节的FF。

3.需要使用到的IP核

主要是“ASMI IP核”和“ Remote Update IP核”,还有PLL IP核。PLL不必多说。另外两个IP核配置如下图。

如下面左边图所示,选择要添加的端口。注意“Single byte write”和“Page write”分别表示以“单字节”写入或“多字节”写入。EPCS16是支持多字节写入的,最多可连续写入256个字节,我这里选择的是单字节写入。“Use ‘bulk_erase’ port”和“Use ‘sector_erase’ port”分别表示是以一次性擦除所以扇区和每次只擦除一个扇区。具体内容可参照“Serial Configuration Devices(EPCS1, EPCS4, EPCS16, EPCS64,and EPCS128) Data Sheet”和“ASMI Parallel Intel® FPGA IP Core User Guide”这两个文档,在ALTERA官网可以找到,里面有具体的读,写,擦除的时序图。

REMOTE IP核配置如下图,最好将 “Enable reconfig POF checking”选上,这是该IP核的一个功能,当触发重配置,该功能会校验指定重配置地址的镜像文件是否是有效地,这一点至关重要,后面讲实现思路时再具体讲为什么一定要这个功能。

前面提到过ASMI IP核主要实现读写配置存储器EPCS16,这个IP核就是用来擦除,写,读EPCS16,我们通过这个ip核,不用再管对EPCS16擦除,写,读的时序,EPCS16的擦除,写,读时序也并不复杂,完全可以直接写,在EPCS16手册里有详细的时序图,但推荐使用asmi ip核,因为要使用remote update ip核的“pof_error”功能,必须要使用asmi Ip核。在“Remote Update Intel® FPGA IP User Guide”手册里有详细介绍。

这里再简单交代一下配置remote ip 核代码的流程。

remote ip核发起重配置需要一段代码来实现,主要内容就是指定重配置地址,然后发起重配置。

4.功能实现思路

一个完整的远程系统升级应该包括两个工程文件。一个出厂配置工程,一个应用工程。两个工程分别在EPCS16中所占的储存空间是 0x0 ~ 0x5FFFF,0x60000 ~ 0x1FFFFF。FPGA一上电,就会加载0地址处的配置文件,配置电路。这个时候FPGA跑的就是出厂配置工程。

出厂配置工程的代码逻辑:

1.第一步执行发起重配置,将0x60000地址后的代码配置到FPGA中。这个时候就需要用到pof_error校验的功能,在发起重配置的congfig信号发出之前,检验一下指定地址的配置文件是否完整可用。若证实可用,才发起重配置。若不可用就不发起重配置。因为如果重配置失败,这时候FPGA内部机制决定会继续发起重配置,但是配置文件是不完整的,就会一直发起在重配置,就死掉了。实测证明,只要勾选了pof_error校验的功能,不管自己是否手动判断pof_error,重配置时都会进行校验,如果重配置失败,就不会再发起重配置,当前FPGA依然是当前配置的电路,还可以正常工作,这时候就可以继续烧写新的配置文件。那么为什么第一步就要发起重配置,因为我们采用的是出厂配置工程+应用工程的结构。这样做的原因是为了应对在升级过程中发生断电,若断电,那么配置文件就会不完整,就死掉了。但采用这种方法,升级过程中,出厂配置工程始终没有被修改,因为我们升级的配置文件是从0x60000开始的,至少可以保证还可以再次升级。那么既然应用工程在0x60000地址处,而一上电配置的电路又是出厂配置文件,那么出厂配置文件里第一步就应该进行重配置。这一步重配置若成功,则FPGA里配置的电路就是我们的应用工程了。若失败,则到出厂配置工程第二步。

2.第二步接受串口/网口之类的数据,并将数据写到EPCS16里。数据烧写完成,再发起重配置,配置应用工程到FPGA里。如果这个时候配置又失败了,那么继续烧写数据到EPCS16里,直到数据烧写无误,烧写数据可以采用一些校验手段,一帧一帧的收收据,写到EPCS16里。

上面是情况是指应用工程所在地址配置文件是无效的。当应用工程本就是正常使用的,只是当前需要升级新的程序了。那么一上电,还是会先配置出厂配置工程,配置完成又配置成应用工程。最后在FPGA里跑的电路是应用工程,那么就要求在应用工程也需要有接受串口/网口数据,烧写EPCS16的功能,几乎需要将出厂配置工程里的功能都要加到应用工程里。但应用工程里不再需要重配置功能了,应用工程在没有收到更新的请求时,正常跑应用电路,在收到应用更新请求时,更新应用工程。

5.小结

本文主要描述了在线升级里用到的两个IP核和我书写该代码时的方法逻辑。至于串口/网口接收数据,接收数据过程中防止收错数据、漏收数据的校验方法,烧写擦除EPCS16,没有过多介绍。

注意

1.本文提到的两个IP 核工作频率限制在20M以内。

2.EPCS16在写之前要先擦除,否则可能写入失败。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)