【国产复旦微FMQL45教程】-Procise应用流程

(2)弹出的窗口里,设置“File Type”为“Verilog”,“File Name”为“led_procise”后点击“OK”即完成了文件的添加。(2)弹出的窗口里,设置“File Type”为“UCF”,“File Name”为“led_procise”后点击“OK”即完成了文件的添加。(4)Device Family 里选择“FMQL”,Device 选择“45”,然后点击“Next”。

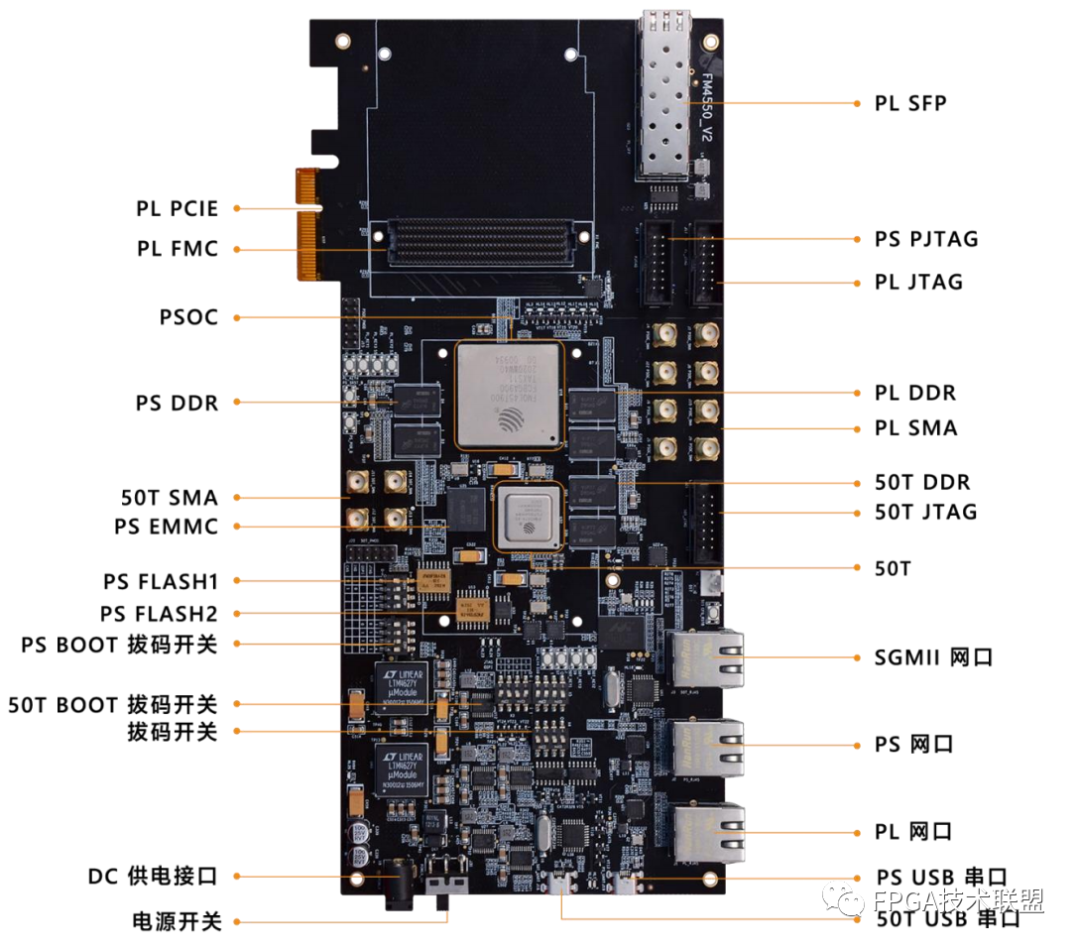

本教程采用 FMQL7045 FPGA开发板来完成整个试验,板卡照片如下:

具有丰富的接口资源,系统框图如下:

本教程用于完成基于Vivado的FMQL45的LED实验,目标是能够将这款开发板PL端先跑起来。

2 Procise工程建立

(1)在Windows 中可以双击 Procise 快捷方式启动 Procise。

(2)在 Procise 开发环境中点击“New Project”可以创建一个新工程。

(3)在弹出的对话框中输入工程名和工程存放路径,我们这里取名叫 led_procise。

需要注意工程路径“Project location”中不能有中文空格,路径名最好也不要太长。

然后 Procise 的工程 Name 的首字母不能是数字。然后点击 Next。

(4)Device Family 里选择“FMQL”,Device 选择“45”,然后点击“Next”。

(5)下一步会让我们选择是否添加已有的文件到工程,我们这里不添加,直接选择“Next”。

(6)点击“Finish”即可完成“led_procise”工程的创建。

(7)下图为 Procise 的软件界面。

3 创建Verilog HDL文件

(1)右键点击 Sources 图标,选择添加或者创建设计源文件“New Source”。

(2)弹出的窗口里,设置“File Type”为“Verilog”,“File Name”为“led_procise”后点击“OK”即完成了文件的添加。

(3)添加完成后会自动弹出.v 文件的编辑界面。

(4)编写一段“led_procise.v”逻辑代码,这里定义了一个 32 位的寄存器 timer,用于循环计数 0~499999999(1 秒),计数到 499999999 的时候,timer 变 0,并翻转8 个 LED 灯。

在硬件上表现为 LED 会每秒钟切换一次亮灭状态。编写完代码后记得保存,源代码如下图:

4 添加约束文件

(1)右键点击 Constrains 图标,选择添加或者创建设计源文件“New Source”。

(2)弹出的窗口里,设置“File Type”为“UCF”,“File Name”为“led_procise”后点击“OK”即完成了文件的添加。

(3)添加完成后会自动弹出.ucf 文件的编辑界面。但是这里是空的,需要我们自己去添加相关的约束。约束格式和 Xilinx 的 UCF 约束格式一致。

(4)在 ucf 文件里手动编写管脚和时钟的约束如下(Procise 不支持界面 GUI 上添加相关约束),保存即可。

5 生成BIT位流

(1)编译过程可以分为综合、布局布线、生成 bit 位流等,这里我们直接右键点击“Generate Bitstream”中的“Run”或者直接双击“Generate Bitstream”就可以直接一键式生成 bit 位流。

(2)如果生成位流成功,下图中所有的步骤都会有绿勾 pass 标志。

6 下载调试

(1)双击“Configure Device”下的“Creat PROM File”。

(2)会弹出下载调试窗口如下。双击其中的“Connect to board”则会出现“Chainconfiguration of your board”及相应的配置图。我们设置的是级联模式,所以会有ARM 和 FM 的 FPGA 配置同时出现。

(3)右键点击 fm7z045 器件,选择“Assign New Configuration File...”,在弹出的窗口里选择生成好的位流(Procise 默认生成位流位置在 rundir 文件夹内),然后点击“OK”。

(4)这个时候可以看到器件上附上了我们的位流文件,右键“Program”即可进行位流下载。

(5)等待下载成功后,我们可以看到 8 颗 LED 灯每秒变化一次,纯 PL 的 Vivado流程至此结束。

8 总结

采用Procise进行FMQL45的开发流程,完成了对LED的点亮。后续会再介绍进一步复杂的教程。

有对这款板卡感兴趣的朋友,可以参考下面的链接,有详细介绍,国产FPGA解决方案,我们是专业的!可支持全国产化FPGA模块的定制、开发和技术服务。

国产化复旦微电子 FMQL45T900 FPGA开发板( 替代Xilinx ZYNQ ARM+FPGA 7045开发板)

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)