ESD及TVS

将ESD静电保护二极管并联于电路中,当电路正常工作时,它处于截止状态(高阻态),不影响线路正常工作,当电路出现异常过压并达到其击穿电压时,它迅速由高阻态变为低阻态,给瞬间电流提供低阻抗导通路径,同时把异常高压钳制在一个安全水平之内,从而保护被保护IC或线路;ESD器件封装的大小从一定程度上可以反应器件的防护等级大小,一般封装越大的器件可容纳的ESD芯片面积也越大,防护等级也越高,反之亦然。VC:钳

1.ESD 基础

1.1 ESD静电二极管工作原理

将ESD静电保护二极管并联于电路中,当电路正常工作时,它处于截止状态(高阻态),不影响线路正常工作,当电路出现异常过压并达到其击穿电压时,它迅速由高阻态变为低阻态,给瞬间电流提供低阻抗导通路径,同时把异常高压钳制在一个安全水平之内,从而保护被保护IC或线路;当异常过压消失,其恢复至高阻态,电路正常工作。

1.2 TVS基本参数

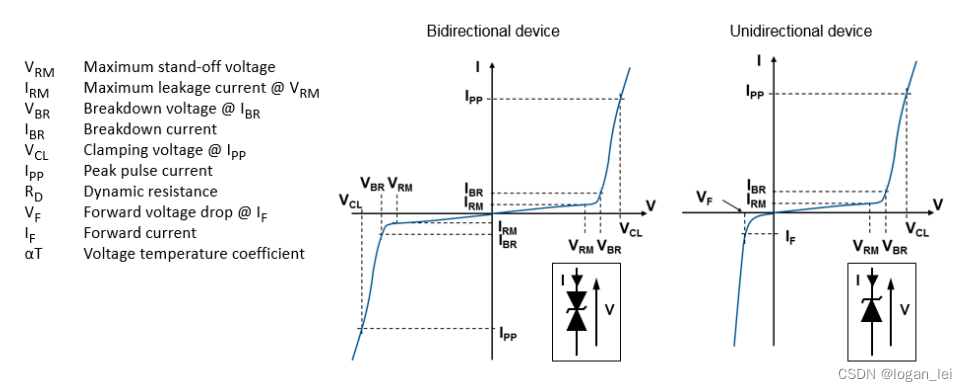

VRM:反向截止电压, 允许长期连续施加在ESD保护器件两端的电压(有效值),在此工作状态下ESD器件不导通,保持高阻状态,反向漏电流很小。

VBR:击穿电压,击穿电压是ESD要开始动作(雪崩击穿)的电压,一般在规定的电流下测量,通常在大小为1mA的电流下测量。

IR:反向漏电流, 在指定的直流电压(一般指不超过最大工作电压)的作用下,流过ESD器件的电流。一般地,TVS管的反向漏电流是nA级,压敏电阻漏电流是μA级,此电流越小,对保护电路影响越小。

IPP:峰值脉冲电流,ESD产品一般采用8/20μs的波形测量。

Vcl:钳位电压, ESD器件流过峰值电流时,其两端呈现的电压,超过此电压,可能造成ESD永久性损伤。

Cj:PN结的结电容, 在给定电压、频率条件下测得的值,此值越小,对保护电路的信号传输影响越小。比如硅半导体TVS管的结电容(pF级),压敏电阻的寄生电容(nF级) ,另一方面ESD的结电容与ESD的芯片面积、工作电压有关系。对于相同电压ESD产品,芯片面积越大结电容越大;对于相同芯片面积的ESD,工作电压越高结电容就越低。

响应时间(Response Time) 指ESD器件对输入的大电压钳制到预定电压的时间。一般地,ESD管的响应时间是Ps级,此时间越小,更能有效的保护电路中元器件。

2.ESD进阶

2.1 TVS一般选型步骤

1.计算接口信号幅值的范围来确定ESD器件的工作电压,被保护IC的最大工作电压<VRM;

2.根据信号类型决定使用单向或者双向ESD器件;

3.根据信号速率决定该接口能承受的最大寄生电容;

4.根据电路系统的最大承受电压冲击,选择适合的钳位电压,被保护IC的最大可承受电压>Vcl;

5.根据电路设计布局及被保护线路数选择合适的封装。

6.确保ESD器件可达到或超过IEC 61000-4-2 level4。

2.2 TVS闩锁效应

当我们使用具有 SCR (Silicon Controller Rectifier) 结构的ESD保护组件时,其 I-V 曲线具有snap-back的特性。这种结构的TVS的IV曲线如下图所示:

要形成闩锁效应必须透过突波的触发使保护组件进入导通状态,像是ESD、surge、或是EMI造成的感应电压等。如闩锁效应被触发,即使是外界的突波已经衰减,但ESD组件依旧会处于导通的状态,这就是闩锁效应典型的现象。

如果ESD发生之后系统提供足够的bias电压(Vbias)及bias电流(Ibias) 施加在TVS之上,将会使组件继续维持在导通状态无法被截止。同时满足以下两个条件才能使组件维持发生闩锁效应: Vbias > Vhold和Ibias > Ihold。如果要将闩锁效应解除,必须使系统断电,亦或使Vbias < Vhold或是Ibias < Ihold。TVS持续在导通状态会使得电流大量经由TVS流向GND,TVS持续升温甚至烧毁。另一个显著的影响是TVS持续导通,讯号线或电源的电位被箝制在低电压,使得讯号无法正常传输或是电源平面无法达到正常的电压位准造成系统异常。

但如果为了追求更低的箝位电压而使得Vhold < Vbias,TVS 将曝露在发生闩锁效应高风险之下,如下左图所示;确保TVS的Vhold必须大于Vbias以避免闩锁效应风险,如下右图所示。图片来源

2.3 TVS Layout 注意事项

(一)TVS应尽可能靠近外部接口摆放,由图一可见,当TVS摆放位置靠近外部接口(I/O)时,外部能量可以快速经由TVS宣泄至地,此为较佳的摆放方式;但当TVS摆放位置距离外部接口较远时,外部能量有可能造成讯号的扰动,因此造成在TVS起到保护之前,ESD就干扰到整个系统的运作。

(二)TVS应避免走分支路径 当PCB布线空间狭小时,为了方便摆放TVS,有时会将讯号线另外拉线后接到TVS进行使用,如图二(左)。类似此种另加引线的布线方式将导致TVS无法达到最有效的防护效果。通常于TVS建议走线时,都建议将预保护的讯号线直接通过TVS,并且不建议使用而外拉线的方式进行使用。

3.ESD测试

ESD产生的原因多种多样,对集成电路放电的方式也有所不同。为了保证集成电路产品的良率,提高可靠性,需要对集成电路ESD防护能力进行测试。一般可分为两类:样品研究型测试和产品通过型测试。

(1)样品研究型测试:在芯片的研发阶段,与ESD防护研究最为相关的是防护器件的功能测试。此阶段的测试广泛采用传输线脉冲技术(TLP)。通过TLP测试,可以获得防护器件的关键性能参数,便于在生产制造过程中调整相关的设计,从根本上提高产品的ESD防护能力,保证良率。

(2)在产品通过型测试中,为了更好地量化不同情形下的ESD冲击,一般分为五种不同的模型。包括工业界作为产品片上ESD等级衡量标准的HBM,CDM,MM模型和针对板级和系统级ESD防护的IEC(International electrotechnical commission)模型和HMM人体金属模型(Human metal model)。

ESD测试在操作上分为接触放电(Contact discharge)和空气放电(Air discharge),一般的判断标准是:

接触放电 - 外漏金属表面,外漏接口,如USB接口,人体能够触摸到的地方;

空气放电 - 外漏金属部分,外漏接口,如USB接口,人体够触摸到的地方;Mic孔,Spk卸声孔,其他slot缝隙,能够空气放电的地方。

3.1 ESD测试模型

3.2 ESD测试设备

3.3 ESD测试标准

ESD测试标准和方法 - 北海北的文章 - 知乎 https://zhuanlan.zhihu.com/p/570835421

3.常见场景下TVS器件推荐

USB2.0 Power & Data ESD05V14T-LC(Vcl 较大);

Battery ESD5451N;

uart 1v8 PESD3V3X1BCSF; 3V3 PESD5V0H1BSF;

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)