virtuoso中数模混合版图的lvs教程

virtuoso之混合版图的lvs教程

本文章记录了版图设计过程中关于数模混合版图部分的lvs检查的相关内容

数模混合版图的lvs检查教程

1、数字版图的导入及单独lvs检查

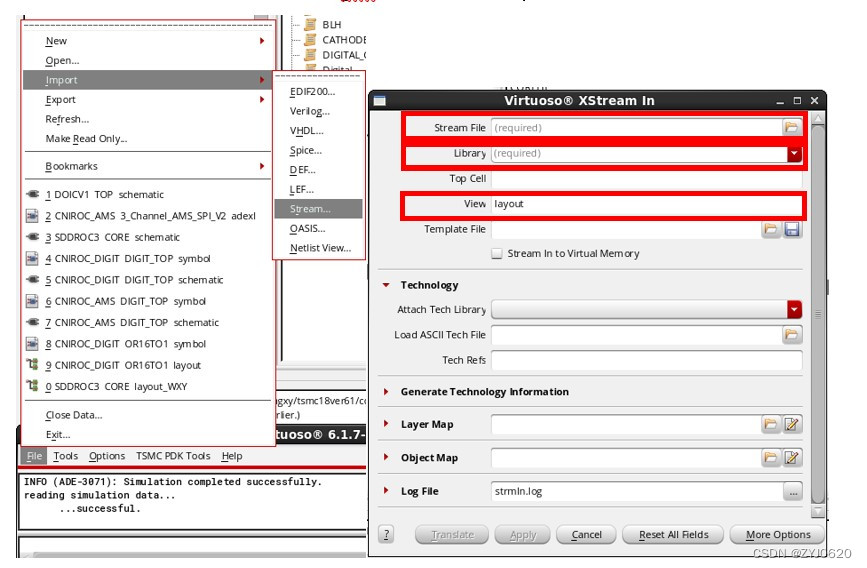

① virtuoso中选择导入stream将gds文件导入,目标库中需包含带layout的数字单元标准库(tsmc18的数字单元标准库文件名为tcb018gbwp7t.v)

stream file选择要导入的gds文件,library选择版图要存放的库,view即版图在库里的名字。设置完毕点击translate即可在库里看到版图文件,cellview的命名与gds文件名相同

② 数字综合版图时不区分label的drawing和pin,所以我们需要关注数字版图中的pin脚是否为metal pin类型,如果不是则需要逐一修改为pin类型

③ 在cadence进行drc与lvs检查。drc检查与模拟相同,此处不做赘述

模拟版图在做lvs检查时,网表由schematic原理图生成,而数字的原理图在cadence里并没有生成,所以我们取消lvs窗口下input-netlist中export from schematic的勾选,并将sprce file选择为实际使用的cdl文件的路径。

额外需要说明的是,若数字综合与模拟不在同一台机子上完成,则需要将数字版图的cdl文件里的include 的路径修改为tcb018gbwp7t_270a.spi在cadence里实际存放的路径

2、数模混合版图修改网表进行lvs检查

① 运行lvs,勾选export from schematic viewer提取原理图网表文件

② 修改数字网表cdl文件:将原理图提取网表中的数字电路模块的端口列表拷到cdl文件中,替换原来的声明端口列表(SUBCKT),注意要将数字电路网表中port的“< >”括号改成“[ ]” ;若有不止一个的数字模块则都需要修改。

修改模拟部分的网表也是可以实现lvs检查的,但由于模拟部分的声明调用复杂所以选择修改数字模块的网表来使两者的调用顺序对应

③ 将核心电路所用到的数字模块的cdl文件包含到提取的网表中(include)LVS的netlist中取消勾选从原理图产生网表,使用修改好的网表重新运行LVS。

3、介绍cadence中lvs box的使用

本节说在前面的是,lvs box的使用只能检查出版图中被看作黑盒部分的pin脚连接的正确与否,其余部分与黑盒的连接关系不作检查;目前证实的是box部分内部短路以及box与其余电路的连接短路没有办法查出来,存在使用风险,若box部分的版图已经绘制好不建议使用lvs box,会隐藏一些潜在风险,建议替换网表进行lvs检查。

接下来根据原理图名与版图名相同与否进行介绍

① 在 LVS Options→include 中勾选 Include Rule Statements,若版图名与原理图名对应相同则输入:LVS BOX XXX (XXX);Run LVS 结果会有 BOX 单元提示。单元显示空心则表示lvs检查通过

② 若版图与原理图的名字不一致。例如如版图的名称是inv_box,但电路依然为inv,这种情况需要使用到 H-cells。首先需要创建一个 hcell 文件,按照格式:[版图名] [空格] [电路名]的格式输入信息。

在 Inputs→H-Cells 中勾选 Use H-Cells file,并选择上述的 hcell 文件。

同时需要修改 LVS Options→include→Include Rule Statements 信息。

③ 匹配多个不同名的版图和同一个电路。同一个 inv 可能由于版图的形状不同等原因存在不同名的单元,假设电路inv,版图有inv_box和inv_ip。在上一种情况的基础上修改 hcell 文件。

修改 LVS Options→include→Include Rule Statements 信息。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)