高速Serdes技术(FPGA领域应用)

SERDES,即 Serializer / Deserializer,是串行器和解串器,是一种广泛应用于高速串行数据传输的技术。它将并行数据序列化成一个高速串行数据流,并在接收端将该序列还原为原始的并行数据。SERDES 技术通常使用在点对点传输场景下,例如在芯片之间、板卡之间或机箱之间,因为这些场景需要传输大量的数据以及较长的距离和高速率。SERDES 技术可以通过降低线路数量和减小线路长度来提

目录

引入

回顾接口技术发展历史,其实数据的传输最开始是低速的串行接口(Serial Interface,简称串口),为了提高数据的总带宽,首先想到的是增加数据传输位宽,再进一步提升速率。也就是并行接口(Parallel Interface,简称并口)的方式,并逐渐取代传统低速串口成为主流。但随着并口的发展,其限制也也越来越明显。而高速串行(High Speed Serial ,HSS)接口技术具有的优势使其有取代目前并口的趋势。表现为接口总带宽的显著提升。其历史就像从山间小道升级为乡村公路,再到高速公路(网),能够提供更高的通行量。

目前并口发展遇到的限制主要为,一方面芯片封装面临着IO数量紧张的问题,另一方面是,并口的数据速率提升过程中面临的串扰(Crosstalk)和噪声(SSN)问题,使得数据的同步变得很困难。

一、Serdes(概念-历程)

1、概念

SERDES,即 Serializer / Deserializer,是串行器和解串器的简称,是一种广泛应用于高速串行数据传输的技术。它将并行数据序列化成一个高速串行数据流,并在接收端将该序列还原为原始的并行数据。

SERDES 技术通常使用在点对点传输场景下,例如在芯片之间、板卡之间或机箱之间,因为这些场景需要传输大量的数据以及较长的距离和高速率。SERDES 技术可以通过降低线路数量和减小线路长度来提供高速、可靠的数据传输。

SERDES 技术通常由两个部分组成:serializer 和 deserializer。serializer 用于将内部的并行数据序列转换为高速串行数据流,而 deserializer 则将收到的高速串行数据流转换回原始的并行数据序列。在 SERDES 技术中,还包括时钟恢复电路和同步电路,以确保正确地复原数据。

SERDES 技术广泛应用于现代通信、网络、存储等领域,例如 PCI Express、SATA、USB3.0 等标准都采用了 SERDES 技术,以提供高速、可靠的数据传输。

2、技术现状

SERDES 技术在现代通信、网络和存储系统中得到了广泛应用。随着数据中心和云计算的普及,高速串行接口的需求越来越大,因此 SERDES 技术在这些领域的地位也越来越重要。

近年来,SERDES 在以下方面得到了进一步发展:

更高的数据传输速率:SERDES 技术已经能够提供 10 Gbps 甚至更高速率的数据传输,例如 PCIe 4.0 和 5.0 标准采用了 16 GT/s 的速率,使得高性能计算和数据中心应用获得更好的性能和响应速度。

更低的功耗和成本:随着技术进步和集成度的提高,器件的功耗和成本也在逐步降低。例如,现代 FPGA 中的 SERDES IP 核已经能够在低功耗和高带宽的情况下实现千兆位每秒(Gbps)以上的数据传输。

更高的可靠性和抗干扰能力:SERDES 技术的电路设计和信号处理算法也在不断优化,以提高其可靠性和抗干扰能力。例如,采用前向纠错码(FEC)技术或自适应均衡器等技术,可以提高数据传输的可靠性和抗干扰能力。

SERDES 技术在高速串行接口领域的地位越来越重要,它将继续发挥重要作用,推动数据中心、云计算和大数据等领域的发展。

3、发展历程

SERDES 技术的发展历程可以追溯到 20 世纪 80 年代后期,当时在高速串行通信中已经开始采用 SERDES 技术。以下是 SERDES 技术发展的主要历程:

1990 年代初:SERDES 技术在存储器领域的应用

首先,在存储器领域中使用 SERDES 技术,例如高端磁盘阵列、SAN 等存储设备。这些设备需要高速传输大量的数据,并需要采用高速串行接口来实现较长的传输距离。

1990 年代末:SERDES 技术在网络通信领域的应用

随着互联网和局域网技术的发展,网络通信成为 SERDES 技术的另一个重要应用领域。在这个时期,SERDES 开始在多种网络标准中得到广泛应用,例如 Gigabit Ethernet、Fibre Channel 和 InfiniBand 等。

2000 年代:SERDES 技术在计算领域的应用

随着计算机系统性能的提高,计算领域也开始采用 SERDES 技术。例如,PCI Express 和 Serial ATA 就是基于 SERDES 技术的高速串行接口标准,以提供更高的数据传输速率和更好的性能。

当代:SERDES 技术的新进展

随着技术的发展和应用领域的扩展,SERDES 技术依然在不断发展。例如,采用前向纠错码(FEC)技术或自适应均衡器等技术,可以提高数据传输的可靠性和抗干扰能力。同时,SERDES 技术还在不断提高数据传输速率、降低功耗和成本,并扩展应用于各种领域和场景中。

SERDES 技术不断发展和创新,为现代高速串行通信、网络和存储设备提供了重要的支持和推动。

目前市场上SerDes的应用,主要有Chip-to-Chip,Board-to-Board, Box-to-Box等形式,如图7(a/b/c)示意图。并在大型数据中心,通信骨干网络,消费电子等场景下都有应用。

二、Serdes结构

其结构主要包括以下几个部分:

时钟恢复模块(Clock Recovery Module)

时钟恢复模块的作用是从接收到的串行数据中提取时钟信号,以便后续电路正确解析收到的数据。时钟恢复模块通常采用 PLL、DLL 或其他技术实现。

数据编解码模块(Data Encoding and Decoding Module)

数据编解码模块通常用于将发送端的并行数据编码成串行数据,并将接收端收到的串行数据解码为并行数据。常见的数据编解码方式包括 8b/10b、64b/66b 等。

串行器(Serializer)

串行器一般位于发送端,其作用是将并行数据转换成串行数据,并通过串行发射器进行传输。串行器的输出速率取决于时钟频率和数据编码方式等参数,通常可以达到数十 Gbps。

解串器(Deserializer)

解串器一般位于接收端,其作用是将接收到的串行数据转换为并行数据进行处理。解串器通常包括数据解码、时钟恢复、数据缓存和对齐等部分,可以实现高速、稳定的数据传输。

时钟校正(Clock Correction)

在高速串行通信中,由于发送端和接收端时钟的不完全同步,数据可能会出现位移和抖动,导致误码率增加。为了解决这个问题,可以采用Clock Correction技术,该技术会利用特定的算法来对接收端的时钟进行校正,以使其与发送端的时钟同步,从而能够更准确地接收数据。

通道捆合(Channel Bonding)

是一种将多个物理通道绑定在一起,形成一个逻辑通道的技术。在SerDes(串行器/解串器)中,它可以通过将多个高速串行通道捆绑在一起,实现更高带宽的传输。这样做可以显著提高通信速度,并减少通道占用的物理空间。同时,它还有助于提高数据的可靠性和容错性,因为即使其中一个通道发生故障,整个系统仍然可以继续工作。

SERDES 的结构主要包括时钟恢复模块、数据编解码模块、串行器和解串器等部分,是现代高速串行通信和存储设备中不可缺少的关键技术。

三、在FPGA领域中的运用

在 FPGA 领域中,SERDES 技术主要应用于高速串行通信和存储接口等方面:

高速串行通信

SERDES 可以将 FPGA 内部的并行数据转换成高速的串行数据,通过 PCB 等介质进行传输,然后再将其转换为并行数据进行处理。这种方式可以大幅提高数据传输速率,降低功耗和硬件成本,特别是在高速网络、光纤通信等场景中具有很大的优势。

存储器接口

SERDES 还可以用于连接 FPGA 和高速存储器(如 DDR3/4),实现高速、稳定的数据传输。在这种场景下,SERDES 可以充分利用存储器接口的带宽,提高存储器读写速度和系统吞吐量。

视频信号处理

SERDES 技术也广泛应用于视频信号处理领域。例如,在 HDMI 接口中采用了 D-PHY 或者 TMDS(Transition minimized differential signaling,过渡最小化差分信号)等 SERDES 技术,可以实现高清视频数据的传输与显示。

高速总线接口

SERDES 还可以用于 FPGA 与其他高速总线接口(如 PCI Express、SATA 等)的连接。它可以将 FPGA 内部的数据转换为这些接口所需的串行数据格式,实现 FPGA 与外部系统之间的高速数据传输。

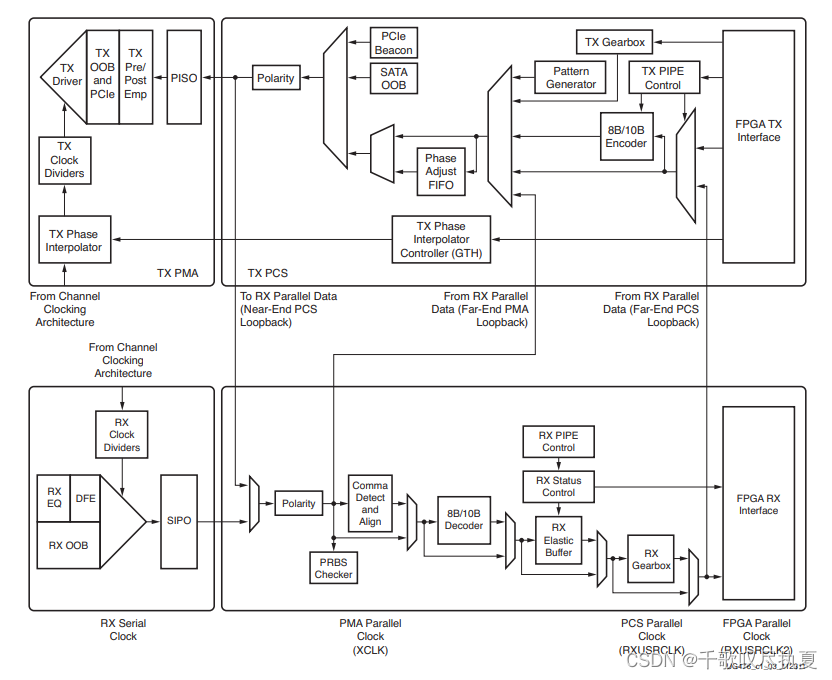

Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SerDes(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路,为各种高速串行数据传输协议提供了物理层基础。MGT收发器的TX发送端和RX接收端功能独立,而且均由物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层(Physical Coding Sublayer,PCS)两个子层组成,结构如下图所示。

PMA子层内部集成了高速串并转换电路,预加重电路、接收均衡电路、时钟发生电路和时钟恢复电路。串并转换电路的作用是把FPGA内部的并行数据转化为MGT接口的串行数据。预加重电路是对物理连接系统中的高频部分进行补偿,在发送端增加一个高通滤波器来放大信号中的高频分量进而提高信号质量,但预加重电路会导致功耗和电磁兼容(Electro Magnetic Compatibility,EMC)增加,所以如非必要一般情况下都把它屏蔽掉。接收均衡电路主要用来补偿由频率不同引起的阻抗差异。时钟发生电路与时钟恢复电路在发送端把时钟和数据绑定后发送,在接收端再从接收到的数据流中恢复出时钟,这样可以有效地避免在高速串行传输的条件下时钟与数据分开传输带来的时钟抖动问题。

PCS子层内部集成了8B/10B编/解码电路、弹性缓冲电路、通道绑定电路和时钟修正电路。8B/10B编/解码电路可以有效的避免数据流中出现连续的‘0’或者‘1’,以保证数据传输的平衡性。通道绑定电路的作用是通过在发送数据流中加入K码字符,把多个物理上独立的MGT通道绑定成一个时序逻辑上同步的并行通道进而提高传输的吞吐率。弹性缓冲电路用来解决恢复的时钟与本地时钟不一致的问题并可以通过对缓冲区中的K码进行匹配对齐来实现通道绑定功能。

具体的时序分析,可以参考Xilinx 有关 serdes的文档(第五节,我列了相关文档)

下图是一个N对SerDes收发通道的互连演示,一般N小于4。

可以看到,SerDes不传送时钟信号,这也是SerDes最特别的地方,SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR从数据的边沿信息中抽取时钟,并找到最优的采样位置。

SerDes采用差分方式传送数据。一般会有多个通道的数据放在一个group中以共享PLL资源,每个通道仍然是相互独立工作的。

SerDes需要参考时钟(Reference Clock),一般也是差分的形式以降低噪声。接收端Rx和发送端Tx的参考时钟可以允许几百个ppm的频差(plesio-synchronous system),也可以是同频的时钟,但是对相位差没有要求。

作个简单的比较,一个SerDes通道(channel)使用4个引脚(Tx+/-,Rx+/-), 目前的FPGA可以做到高达28Gbps。而一个16bits的DDR3-1600的线速率为1.6Gbps*16 = 25Gbps,却需要50个引脚。此对比可以看出SerDes在传输带宽上的优势。

相比源同步接口,SerDes的主要特点包括:

SerDes在数据线中时钟内嵌,不需要传送时钟信号。

SerDes通过加重/均衡技术可以实现高速长距离传输,如背板。

SerDes 使用了较少的芯片引脚

四、Serdes跟Lvds的关系

看了这么多,也许你会疑惑,Serdes跟Lvds怎么会这么像?他们的区别是什么?

SERDES 和 LVDS 都是用于高速数字信号传输中的技术,其中 LVDS 是 SERDES 技术中常用的差分传输方式之一。

SERDES 技术是一种将并行数据转换为串行数据,并使用差分信号进行传输的技术。而 LVDS(低电压差分信号)是指通过比较输入的两个不同电压来传输数字信号的技术,其核心原理是采用对称式多段放大器保证差分信号的可靠传输,能够有效抵抗电磁干扰、噪声等干扰信号的影响。

在实际应用中,SERDES 技术中的差分传输方式可以选择多种信号差动标准,其中 LVDS 便是其中一种应用广泛的标准。例如,在一些高速信号处理系统和通信领域中,SERDES 技术一般使用 LVDS 标准来传输差分信号,因为 LVDS 有许多优点,如具备较小的共模噪声、抗干扰性能强、功耗低等。因此,SERDES 技术与 LVDS 技术是紧密相关的,LVDS 技术也是 SERDES 技术中常用的差分传输方式之一。

五、Xilinx 有关 serdes的文档

Xilinx 官网提供了多份文档详细介绍 7 系列 FPGA 的 SERDES 结构和应用,以下是其中的几份:

7 Series FPGAs GTX/GTH Transceivers User Guide (UG476)

这份用户指南详细介绍了 Xilinx 7 系列 FPGA 中采用 GTX/GTH Transceiver 的 SERDES 结构,包括通信接口、时钟频率、数据编解码、时钟恢复等方面的内容。此外,该文档还介绍了如何使用 Vivado Design Suite 进行电路设计、实现和验证。

7 Series FPGAs Transceivers Wizard User Guide (这个文档,现在并入在UG476,在第27页)

这份用户指南主要介绍了使用 Xilinx Transceivers Wizard 工具进行 7 系列 FPGA SERDES 的配置和优化。该文档详细说明了 Transceiver Wizard 工具的使用方法、支持的协议、性能参数等方面的内容,并提供了示例设计和实验步骤。

7 Series FPGAs SelectIO Resources User Guide (UG471)

这份用户指南主要介绍了 7 系列 FPGA 中采用 SelectIO 技术的 SERDES 结构。该文档详细说明了 SelectIO 数据编解码、时钟恢复等方面的实现方法和技巧,同时还提供了多个使用案例和设计建议。

7 Series FPGAs PCB Design Guide (UG483)

这份 PCB 设计指南主要介绍了在 7 系列 FPGA 中设计 SERDES 时需要注意的 PCB 布局和布线规范。该文档详细说明了 PCB 信号完整性、EMI 抑制、时钟分配等方面的实现方法和技巧,同时还提供了多个设计建议和最佳实践。

六、参考文献

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)