PCIe 5.0 金手指layout 设计规范

AIC金手指区域必须设计内层GND平面,以屏蔽金手指两面的串扰,这些平面从金手指北侧向外延伸1.5mm到金手指下方区域,能够有效覆盖金手指的上方1.5mm长度,屏蔽了连接器接口Tx和Rx主要的近端串扰(NEXT)。AIC应该在靠近倒角位置布置间隔1mm的GND孔,这些地孔通过和内层的GND平面相连,进一步抑制金手指边缘区域的串扰。这些过孔有效地镜像了金手指北侧的地孔。在金手指的最中间层,向外延伸3

PCIe CEM规范允许两种不同的AIC金手指设计,一种是满足32.0 GT/s的要求,另一种是用在16.0 GT/s及以下的情况。

首先说一下第一种情况,“Full Core Shielding Planes with Fingertip South Vias” 即在金手指的内层将地平面铺到金手指边缘的地孔位置(结合后面的图更易于理解)。在PCIe5.0链路中必须使用此设计,在PCIe4.0及以下链路中推荐使用此设计。

这种布局通过金手指区域中的PCB内层GND平面,显著减少了高速Rx和Tx通道之间的近端串扰(NEXT)。这显著提高了信道性能。然而,必须仔细注意布局要求。

为了满足信号完整性,需要做如下布局:

1.金手指最中心的内层GND层需要延伸到南侧的金手指边缘;

2.金手指北侧(靠近板内)的GND孔要接到金手指的地平面,相邻的接地过孔通过表面蚀刻连接。

3.类似的过孔阵列被添加到金手指的南侧(靠近板边),这些过孔连接金手指内部的接地平面。这些过孔有效地镜像了金手指北侧的地孔。南侧的地孔也是通过表面蚀刻连接。

4.在次外层,南侧的GND孔通过一个Ground Bar连接在一起。

金手指尺寸:

PCIe5.0的金手指宽度为0.6mm,PCIe4.0的金手指宽度为0.7mm

长度有两种,所有的GND pad长度为3.2mm,紧靠南部连接的过孔,其他的包含高速PCIe信号、电源、Sideband、PRESENT1#和PRESENT2#这些pad长度为3mm。

作为对比,PCIe4.0的金手指长度为3.91mm,但PRESENT1#和PRESENT2#是3.2mm。

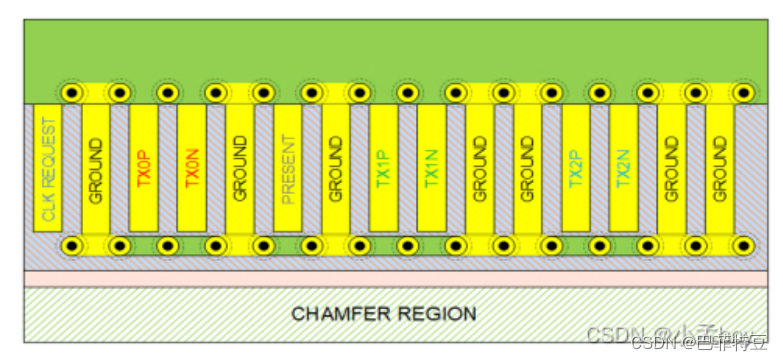

金手指表面分布

相邻的金手指地孔:

CEM规范要求在金手指邻近区域布局GND孔。过孔需要分布在金手指的间隙,这些地孔可以抑制连接器接口中存在的接地谐振。PCIe 5.0 CEM规范要求在金手指pad之间的每个间隙上方放置一个接地过孔,就是沿AIC金手指pinfield(例如,x16连接器中的位置A12/B12到A82/B82)间隔1mm的均匀接地过孔阵列。这和PCIe4.0的要求不同。金手指的A1/B1-A11/B11可以不加这些地孔,因为没有高速信号,但是加了也没事。

尽管建议使用直径为8mil(或更小)的钻头,但这些相邻的金手指接地通孔不会阻碍从金手指通孔/pad旁边引出的走线。较小的钻头和孔盘通常会留下较大的间隙,并允许地面过孔之间的信号更容易逸出。从过孔区域引出时需要一小段单端走线。注意:

1.两到三个相邻的地孔pad应该连在一起,保留间隙允许走线从信号pin引出。

2.靠近板内的金手指GND孔应该尽量靠近金手指的pin,并放置在pin间隙的正中间。

3.建议钻孔尺寸为8-10mil,因为并不影响最终效果,并不一定要使用特殊的钻孔尺寸。

标金手指地孔分布,高亮了出线

Note:尽量将地孔pad连在一起,保留信号出线间隙。

金手指核心屏蔽层面

金手指下方区域必须要有内部的平面层,以抑制PCB正面和背面指边之间的串扰。这些核心屏蔽层分布在最里面的层面,举个例子,一个10层的叠层,那么屏蔽层应该是5&6层。这些层延伸至金手指区域3.91mm,超出金手指pin。覆盖金手指pin的3mm长度,并连接到金手指尖的南侧GND孔。这些层屏蔽了连接器表面所有Rx和Tx之间的近端串扰。从信号完整性角度考虑,这些层距离金手指外表面至少要0.52mm(21mil),或者换一种说法,这些层必须在金手指厚度1.57mm的中间1/3厚度范围内。这些层可能是距离表面距离大于0.52mm的5mil core的两个表面。只需要两个层面作为屏蔽层。其他的内层金属层应该在金手指的北侧(靠近板内侧),避免和板边的GND bar连接。

金手指南侧(靠近倒角)的GND孔

AIC应该在靠近倒角位置布置间隔1mm的GND孔,这些地孔通过和内层的GND平面相连,进一步抑制金手指边缘区域的串扰。这些地孔仅应该分布在高速pin的区域,即A12/B12到A82/B82。

注意,这些南侧的地孔严禁用在电源和低速pin上,即从A1/B1-A11/B11,以便最小化GND和PWR短路的风险。

和北侧的GND孔要求一样,并不指定南侧GND孔的钻孔尺寸,因为并不影响性能。但是推荐较小的钻孔尺寸和pad尺寸,可以减小PCB制造和可靠性的复杂程度。

南侧的GND孔必须使用和pad直径宽度一样的走线连接,如0.5mm或20mil。

pad的上边缘应该和3.2mm的pin下边缘对齐。

在次外层,需要设计一个长条形的GND bar,将南侧的GND孔连在一起。

在金手指的最中间层,向外延伸3.91mm的GND平面可以经过南侧的GND孔覆盖到金手指的边缘,这样可以提供表层Tx和底层Rx之间的串扰屏蔽。

Plating Tie Bar Removal & metal exclusion region

在金手指加工流程中,需要Plating Tie Bar实现镀金和硬金镀镍,但是在加工流程完成后需要把这些Tie Bar移除,在倒角区域和金手指边缘留下1.3mm的表面非金属区域。这可能在电镀流程之后需要额外的PCB加工流程:回蚀。由于回蚀工艺会在金手指的底部留下一个小的残余凸块,因此很难在金指上获得方形边缘。允许Plating Tie Bar中的一些残余金属超出金手指pin底部0.13 mm,进入金属排除区域,如下所示。理想情况下,Plating Tie Bar应较窄,因此突出部分应较小。

移除 Plating Tie Bar可以避免分层造成的连接器短路,保证连接位置的可靠性。另外,也可以通过减小较长的谐振stub以及寄生电容来提升信号完整性。

禁止在金手指区域布局丝印和油墨。

以下介绍适用于16.0 GT/s及以下速率的layout建议。

由于速率降低,布局的要求也会适当宽松,和之前的建议相比:

1. 金手指最中间的GND层可以只覆盖到50%(1.5mm)

2.不需要在次外层布局长条形的GND Bar

3.无需再金手指南侧(倒角侧)增加GND孔。

尺寸方面,金手指宽度0.6mm,适用于所有金手指。金手指长度3.0mm,适用于所有金手指,包括GND、PRESENT1#和PRESENT2#。

Plating Tie Bar移除和非金属区域

相邻金手指GND孔

和板内相邻的GND孔需求和之前的要求是一致的。这些孔不会阻碍从金手指的Pin出线,在通过这些孔间隙区域时需要一段单端的走线。

AIC金手指内部部分铺地

AIC金手指区域必须设计内层GND平面,以屏蔽金手指两面的串扰,这些平面从金手指北侧向外延伸1.5mm到金手指下方区域,能够有效覆盖金手指的上方1.5mm长度,屏蔽了连接器接口Tx和Rx主要的近端串扰(NEXT)。对于信号完整性来说,GND平面必须距离金手指表面0.52mm(21mil),或者换句话说,GND平面必须在金手指1.57mm厚度的中间1/3位置。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)