DDR4信号完整性仿真

使用SystemSI进行DDR的仿真流程,并对常见的问题进行说明。

在硬件电路设计中,DDR一直是电路设计中的难点。目前正在进行DDR4的电路设计,将基本的仿真设计过程进行一下记录。

主流的仿真工具都是支持DDR4的仿真的,目前使用的主力工具为Sigrity及Hyperlynx,下面以Sigrity系统软件为例说明一下DDR仿真的基本流程。

一、Sigrity软件基本思路

在2019版本以前,Sigrity软件提供了两种DDR的仿真流程。

- 使用SPEED2000将PCB导入仿真软件,选择想要的仿真网络,并加载对应DDR控制器及DDR颗粒模型,设置参数后直接进仿真。

- 先提取想要仿真PCB的频域模型,在另一个软件里将提取的PCB、DDR及DDR颗粒模型,按照逻辑关系连接,进行时域仿真。

在较新的2022版本上取消了第一种流程,保留并完善了第二种仿真方法,目前在2022版本上最高可以支持到DDR5 / GDDR6。

二、Sigrity DDR仿真流程

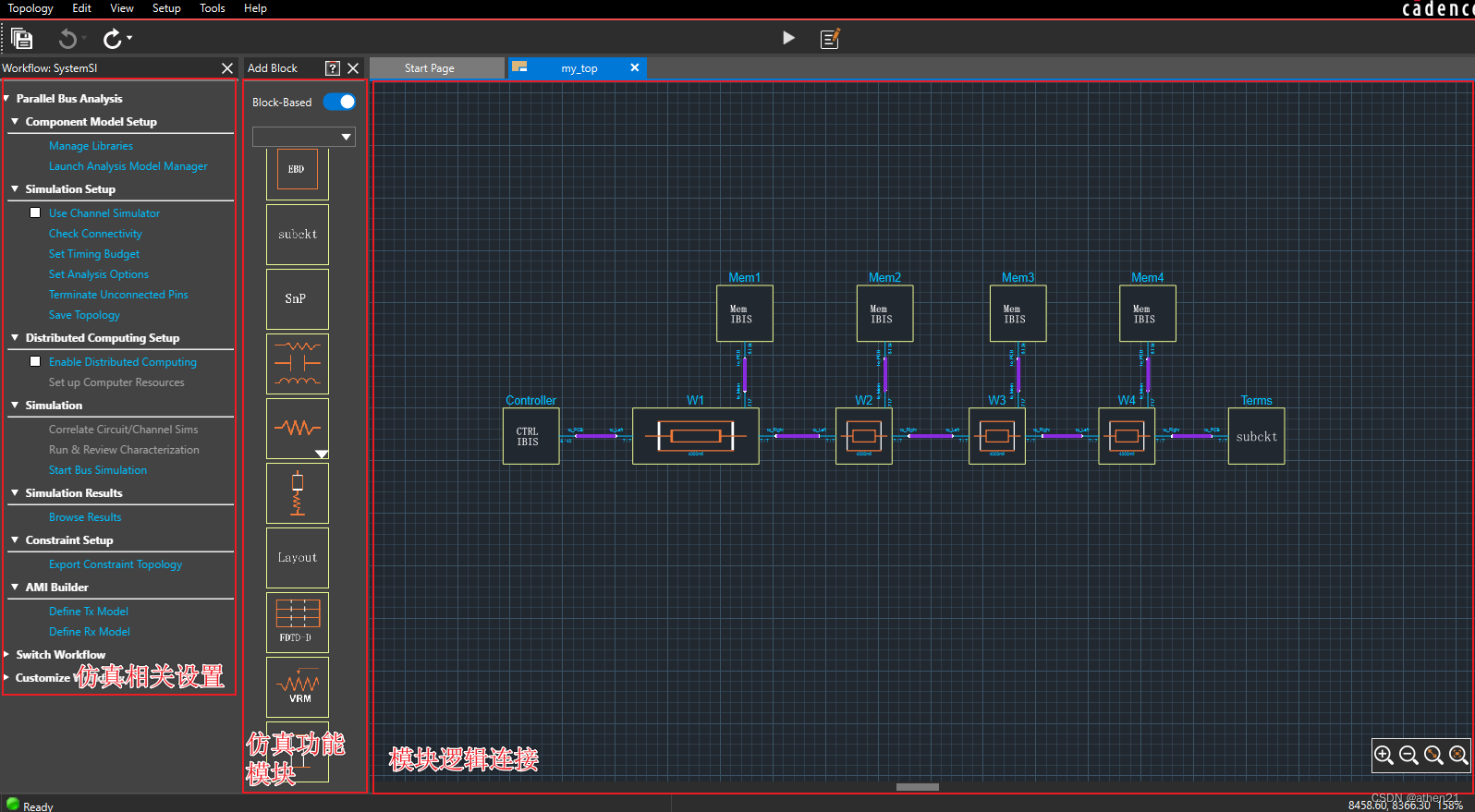

在新的Sigrity软件里,提供了新仿真流程软件SystemSI。在SystemSI里搭建拓扑原理图,软件里提供的PCB Layout模块,可以直接调用求解器,来提取PCB对应仿真网络的模型。模型提取完成,将相关模块按照逻辑连接后,在PowerSI里进行时域波形的仿真。以下对流程详细操作进行说明:

-

打开PowerSI软件,新建仿真拓扑。

-

新建仿真拓扑如下

-

对默认建立的拓扑进行修改

-

通过双击Layout模块加载PCB

-

在Extraction Engine处选择PowerSI,点击Setup Layout按钮,软件会自动调用PowerSI

-

在PowerSI里进行相应的设置后保存,不要点击开始仿真,关闭PowerSI,回到SystemSI界面点击Extract进行参数提取

-

提取完参数之后,按照对应逻辑进行连线

-

连接完成后,左侧Workflow窗口进行设置仿真 ,如果我们只关注信号质量的话,可以只对Set Analysis Options进行设置。其中设置分三个部分:

Circuit Simulation : 选择求解器,选择需要仿真的Corner

Bus Simulation : 选择仿真的总线类型,目前地址线与数据分开仿真,在后续版里会支持同时仿真

IO Models and Stimulus : 设置仿真条件,激励码型,驱动器类型等

-

做完上述设置后点击保存,点击Start Bus Simulation,仿真完成后自动弹出波形查看器。

三、常见问题说明

-

仿真后如何同时得到Die及Package处的波形?

需要在控制器的IBIS模型处勾选 Package Parasitics,位置如下图:

-

激励码型应该如何设置?

激励码型在IO Models and Stimulus进行设置,在Simulus Pattern上点右键,弹出如下窗口:

在上述设置中可设置信号使用同样码型还是不同码型,码型类型支持随机码,伪随机码,自定义码型文件。一般常用的是PRBS7。 -

如何自定义仿真后文件名

在Circuit Simulation的最后一行Simulation Name里,可以勾选自动命名及自定义命名

-

在查看波形眼图时,如何为波形加载眼图模版

可以最上面栏的Mask里自定义眼图模版,但此功能设置麻烦。也可以使用自动生成报告功能,在报告设置项里勾选眼图选项,会自动加载眼图模版,并且会自动调整中心点。

-

有时进行DDR的时域仿真时会仿真失败,波形震荡漂移。

首先,检查设置PCB设计是否正确;其次,查看需要设置的被动器件模型是否设置完成。最后,考虑在PowerSI里提取PCB模型时,是否有加入过大的电容。

四、总结

以上为使用SystemSI进行DDR仿真的一个简要过程,其中还有许多的细节操作许要注意,后其会考虑录制视频效果可能会更好。

掌握仿真工具只是做好信号完整性工作的基础,想要做好DDR信号的设计工作,还需要熟悉DDR相关协议,以及电路PCB等相关知识。在现实中,有多方面的因素会影响到DDR的信号质量,因此,还需要有一定的实验设计及数据分能力,使用最少的仿真组合与时间,寻找到最佳的组合结果。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)