LPC 和 eSPI介绍

LPC总线,原名叫即精简引脚总线,由Intel在1998年引入PC产品,相较于ISA总线,LPC 引脚少,速度快。BIOS串口并口PS/2的键盘和鼠标软盘控制器,比较新的设备有可信平台模块。LPC总线通常和主板上的南桥物理相连,南桥在IBM PC AT平台上通常连接了一系列的“老旧”设备, LPC总线最大的优点是只需要7个信号,在拥挤的现代主板上是很容易布局的随着超大规模集成电路的不断发展,芯片的

eSPI就是SPI升级版?

根据这名字就感觉eSPI就是SPI的升级版,这样说没错。

但是如果你思想上认为只是提高了点速度之类,那你就小看了。

从双向通讯信号上讲,LPC/SPI/eSPI,大同小异、

当我们谈eSPI,其实主要是为了把LPC接口比下去的

eSPI vs. LPC side band信号数量减少

EC/Super I/O芯片和PCH的连接如果用LPC,那么side band信号会多不少,尤其是各种中断信号。因为引入了虚拟中断通讯。#SMI,#SCI,#RCIN这些以前是中断pin脚的,都可以省下来了

CPU与低速外设之间最早是ISA总线,后来被LPC取代,现在LPC也不够看了,eSPI就出现了。

一、什么是LPC

LPC总线,原名叫Low pin count Bus,即精简引脚总线,由Intel在1998年引入PC产品,相较于ISA总线,LPC 引脚少,速度快。

LPC接口是一个低速33 MHz带宽总线,主要在intel.CPU上使用。它是用来连接CPU和外围设备取代工业标准结构(ISA)总线, LPC总线最大的优点是只需要7个信号,在拥挤的现代主板上是很容易布局的。

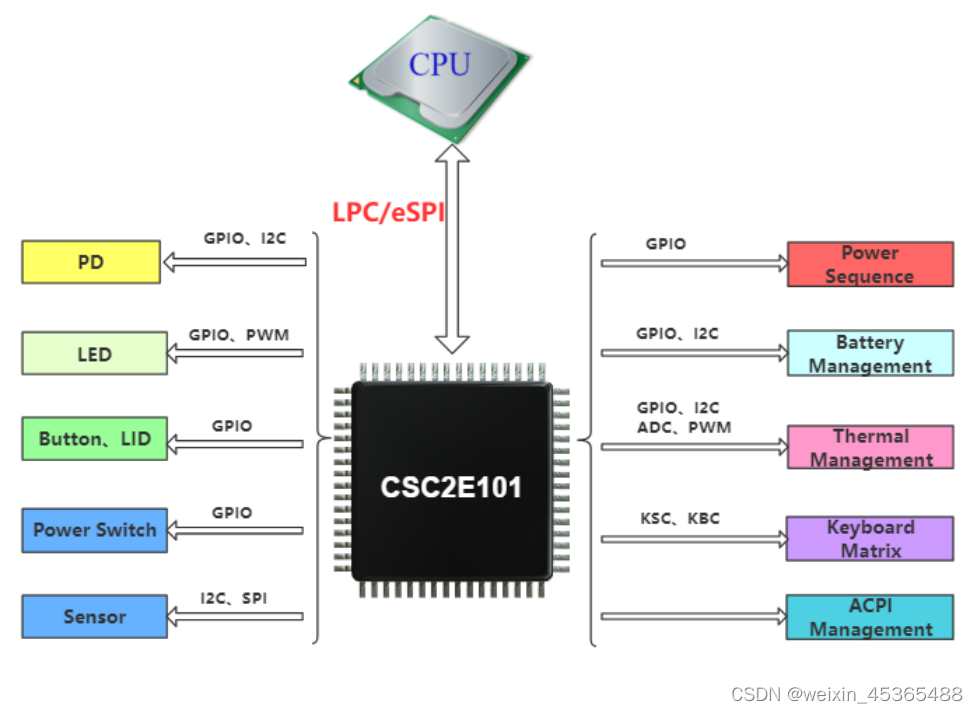

eSPI/LPC专用MCU

嵌入式开发中常见的 I2C、SPI、UART、USB等,都是芯片间的通讯总线。不同协议的通讯总线,是为了解决不同场景、不同需求的数据通讯。 CPU(中央处理器) 和 EC(嵌入式控制器) 之间的通讯也是必不可少的,目前主流的通讯总线有 LPC 和 eSPI。

EC 能够作为一颗专用 MCU,应用在笔记本电脑主板设计中。因为它是一颗携带 eSPI/LPC 外设的专用 MCU。EC 主要的任务就是协助 CPU ,管理一些低速输入设备,比如说鼠标,键盘,EC,SIO以及一些FLASH。采集电池参数、控制主板温度。EC采集到的低速外设信息,就会通过eSPI/LPC传递给CPU。

二、LPC总线

在PC领域, LPC总线用于低速设备(BIOS Flash,Super I/O,TPM)和主板上南桥的连接。

1.LPC总线的接口管脚

LPC总线由7个必选信号和6个可选信号组成,具体如下表所示:

LAD[3:0]是双向信号,传输命令、地址、数据信号

LFRAME_L:表示开始命令

LRESET_L 由CPU的 PLTRST_N信号给出,在逻辑里面复位状态机

LCLK 由 CPU输出33M时钟,和PCI的时钟同源

实例:

CPU端引脚:

MB板上的JDEBUG connector有12pin,没有连接LRESET#信号,只连接了其余的6个必选信号,为主板诊断提供接口,其中CLK_DEBUG由PCH提供,24MHZ:

EC与PCH连接的LPC总线中除了包含7个必选信号,还包含SEEIRQ和CLKRUN#信号。这里需要注意的是JDEBUG的CLK信号与连接EC和PCH的LPC总线中CLK信号并非同一个信号。PCH提供了2个输出24MHz时钟的管脚,但每个时钟只能驱动一个LPC设备,故EC和JDEBUG各连接一个。

2.LPC接口的工作原理

LPC接口的工作原理主要包括数据传输、控制信号和电源供应三个方面。

数据传输方面,LPC接口通过数据线传送数据,可以实现高速数据传输和并行数据传输。

控制信号方面,LPC接口通过控制线发送控制信号,如读写命令、中断请求等,以实现对外设的控制。

电源供应方面,LPC接口通过引脚提供电源供应,保证外设正常工作。LPC接口还支持电源管理功能,可以实现对外设的电源控制和管理。

3. LPC接口规范

LPC接口规范主要包括引脚定义、信号电平和通信协议等方面。

引脚定义方面,LPC接口的引脚分为数据线、控制线和电源线等多种类型,每个引脚都有特定的功能。

信号电平方面,LPC接口的信号电平通常为TTL电平,即0V和5V之间的电压范围,保证了信号的稳定性和可靠性。

通信协议方面,LPC接口通常采用一种特定的通信协议,如I2C、SPI等,以实现数据的传输和控制。

4. LPC接口的通信协议

LPC接口的通信协议是指在LPC接口上进行数据传输和控制时所使用的协议。

常见的LPC接口通信协议包括I2C(Inter-Integrated Circuit)、SPI(Serial Peripheral Interface)等。

I2C协议是一种串行通信协议,通过两根线进行数据传输,支持多个设备共享同一条总线。SPI协议是一种并行通信协议,通过多根线进行数据传输,每个设备都有独立的片选线。

这些通信协议都具有简单、灵活、可靠的特点,可以满足不同应用场景的需求。

LPC总线落伍的原因是:

1,LPC 3.3V的I/O技术,增加芯片的制造成本;

2,LPC只支持33MHz总线时钟,带宽为133Mbps,不能满足新设备的带宽需求,但使用USB3.0/PCIe这类高速接口,成本又太高;

3,CPU芯片组与EC,BMC以及SIO等外设存在大量的边带通信需求,会占用大量的管脚,导致管脚资源成本高。

二、eSPI 总线

eSPI 全称 Enhanced Serial Peripheral Interface,即增强型串行外设接口。eSPI 是为了替代 LPC 而设计。相较于 LPC 总线,eSPI 总线有如下优势:

• 引脚更少,仅 8 个物理引脚

• 功耗更低,电压 1.8V 即可运行

• 速度更快,20-66MHz

• 功能更多,支持 VW、OOB、Flash 等功能

eSPI 通讯总线标准就是根据 SPI 通讯总线标准修改而来。从物理层看,eSPI 总线比SPI 总线多了Rset#、Alert#两个信号,以满足Host复位Slave,Slave向Host发送通讯请求。其他信号,Data-IO、CLK、CS# 没有差异。因此可以说,eSPI 总线和 SPI 总线的物理层完全一致。

如下图所示,是一个 SPI Master 和一个 SPI Slave 的连接框图。

如下图所示,是一个 eSPI Host 和一个 eSPI Slave 的连接框图。

和 SPI 总线一样,eSPI 也支持一主多从,利用 CS# 信号选择不同的 Slave 完成通讯。如下图所示,是一个 eSPI Host和多个 eSPI Slave 的连接框图。

从协议层看,eSPI 和 SPI 通讯协议最主要的差异是,Master 发送和接收之间必须插入一个 TAR 信号,占用 2 个 CLK。即 Master 发送数据转为 Slave 发送数据时,要有一个明显的切换过程。

eSPI 高级功能

通过 eSPI 自定义的命令集,逻辑上可以把 eSPI 通讯总线划分出 4 个数据通道。分别是:Peripheral Channel,VirtualWire Channel,OOB Channel,Flash Channel,以便完成不同类型数据的传输。

如下图所示,是 eSPI Host 和 eSPI Slave 直接通讯的逻辑框图。

PeripheralChannel(外设通道),兼容 LPC 总线上的 Memory Cycle,I/O Cycle 通讯。

VirtualWire Channel(虚拟线通道),进一步减少了 PCH和EC的物理引脚连接,从而降低功耗。

OOB Channel(带外通讯通道)承载 Smbus、PECI等协议。

Flash Channel(Flash通道)传递 FLash“读/写/擦” 操作指令及数据,以支持 MAFs 和 SAFs 两种Flash连接模式。

CSC2E101

芯海科技CSC2E101是一款高度集成的,可灵活配置嵌入式控制器(Embedded Controller),是笔记本电脑、平板电脑、台式机主板上的核心芯片。

CSC2E101采用 32bit 内核,最高主频 60MHz,75DMIPS,内置512K片上Flash作为用户固件存储区域,192KSRAM可以满足客户丰富应用开发的需求。除此之外,该芯片还内置AES/SHA/RSA/ECC硬件安全引擎,为固件安全启动和数据安全提供了坚实基础。

CSC2E101 的 eSPI 模块的设计高度集成,在 HOST 初始化 eSPI 阶段,无需EC固件参与芯片硬件即可自动完成。对于 Peripheral Channel,VirtualWire Channel,OOB Channel,Flash Channel,芯片均提供一组访问寄存器,由 EC 固件管控,完成相应功能。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献26条内容

已为社区贡献26条内容

所有评论(0)