复位电路reset(同步复位,异步复位,异步复位同步释放电路)

异步复位同步释放电路

目录

一、什么是复位电路(reset)

复位电路是一种用来使电路恢复到起始状态的电路设备。一般来说复位电路启动的手段有以下三种:一是在给电路通电时马上进行复位操作;二是在必要时可以由手动操作;三是根据程序或者电路运行的需要自动地进行。

在IC设计中,复位和时钟电路可以说是最为重要的两个电路。这两者主要作用于电路中的时序元件。

二、复位电路的作用

1、仿真过程中:使仿真电路进入初始化状态或者是某种已知的特定状态,基于此状态进行后续的仿真操作。

2、硬件实现中: 在IC设计中,复位信号可以使设计的硬件电路进入一个稳定且确定的状态,避免上电后电路进入随机状态而硬件死机。

【PS:不是所有的设计都需要复位电路,例如(1)组合逻辑不需要复位(2)不需要立刻进入明确状态的电路不需要复位】

三、复位电路的分类

对于电路中的时序元件,把复位信号受到时钟的控制和复位信号不受时钟的控制两种电路分别称为同步复位电路和异步复位电路。如下图:

四、同步复位电路

同步复位即复位信号随着系统时钟的边沿触发起作用。在同步复位电路中,复位信号的本质可以理解为一组数据信号。优先级上是时钟>复位>数据。

同步复位的优点:

(1)一般可以确保电路是一个同步电路

(2)在ASIC设计中,同步电路同步电路一般可以综合为更小的同步触发器(因为触发器没有包含复位逻辑),但是在FPGA设计中并不如此,一般FPGA的时序元件为带异步复位的触发器(也有同步触发器,视厂家而定)。如果在FPGA设计中使用同步复位,其消耗的资源相对较多。

(3)由于触发器的跳转只在时钟的边沿,所以触发器可以在一定程度上过滤电路毛刺。

同步复位的缺点:

(1)较长的保持复位状态时间(至少大于时钟周期)

(2)在低功耗设计中,同步复位一般不能用于门控时钟控制的电路。因为同步复位电路中,主要靠时钟驱动复位和数据。当复位发出时,有可能时序电路此时并没有时钟驱动,那么此时的复位就不能完成。

五、异步复位电路

异步复位电路即复位信号不随着系统时钟的边沿触发起作用。拥有异步复位的寄存器在设计过程中就多了一个引脚(复位引脚)。优先级上是复位>时钟>数据。

异步复位的优点:

(1) 异步复位的复位逻辑和数据逻辑没有任何关系,所以相比同步复位,能够使数据路径更好地收敛。

(2) 不用在时钟的控制下进行复位,所以对于刚才所提到的低功耗设计中,可以达到无时钟复位的效果。

异步复位的缺点:

(1)异步复位不受时钟控制,所以当电路的复位引脚有毛刺时,会引起电路的异常复位。

(2)异步复位时,如果释放复位信号在时钟有效边沿周围。那么可能会引起时序单元的输出出现亚稳态,导致电路亚稳态传播。

六、HDL实现复位设计

在FPGA中应用最为广泛的就是DFF(D触发器),D触发器是一个带有异步复位异步置数的器件。接下来将展示如何使用verilog来描述这个器件。

1、同步复位

always @(posedge clk)

begin

if(!rst_n)

d_out <= 1'b0;

else

d_out <= d_in;

end2、异步复位

always@(posedge clk or negdege rst_n)

begin

if(!rst_n)

d_out <= 1'b0;

else

d_out <= d_in;

end 3、异步复位同步释放

在异步复位时,复位的优先级高于时钟,这样容易造成竞争与冒险,比如当时钟clk的上升沿和复位rst_n的下降沿同时到来时系统应该听谁的,同样也容易造成亚稳态的产生。

亚稳态是指触发器无法在某一个规定时间段内达到一个稳定的可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个期间,触发器输出一些中间级电平或者处于振荡状态,并且这些无效的电平信号会随着电路逐级传递,引发整体系统的不稳定。

在同步复位时,虽然能够有效的解决竞争与冒险的问题,但是从综合得到的电路角度,会多出一个组合逻辑:选择器(MUX),这样会使得资源的浪费。

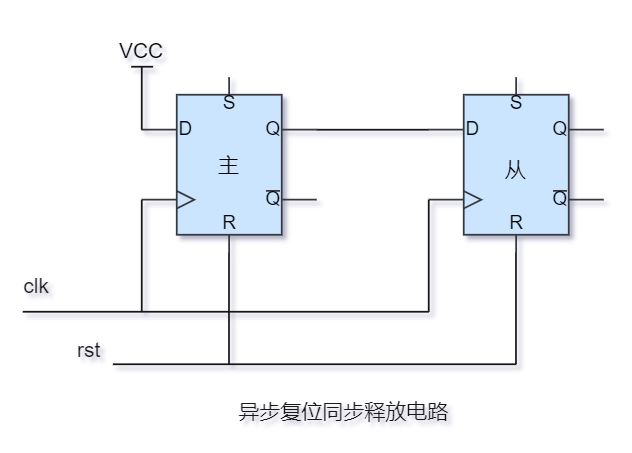

因此,我们需要结合两者,取其所长,引入了异步复位,同步释放电路。电路图如下:

当复位信号被撤销时:此时数据VCC将在时钟的控制下进入主触发器。如果此时复位信号被撤销时候恰好碰到时钟的有效沿引起主触发器的亚稳态。但是此时从触发器在时钟控制下,输入的是主触发器输出的复位稳定值。

复位信号既然对主触发器违反复位时间窗口,对从触发器来说,也一样违反了时间窗口。那从触发器为什么就没有进入亚稳态呢?

对于从触发器来说,rst跳变在其复位时钟窗口内,所以违反了从触发器的复位时间窗口,但对于从触发器,复位前的状态和复位后的状态是一样的。寄存器内部的锁存器不需要跳变来更新自己的状态。所以也就不会因为内部锁存器的电平跳变从而导致亚稳态的发生。

always@(posedge clk or negdege rst_n)

begin

if(!rst_n)begin

rst_n1 <= 1'b0;

rst_n2 <= 1'b0;

end

else begin

rst_n1 <= rst_n;

rst_n2 <= rst_n1;

end

end

在实际的系统设计中,只需要单独编写异步复位同步释放模块,并在系统最顶层完成例化,即可在整体系统中实现以上功能。

七、参考资料

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)