stm32外设-RCC

RCC是Reset and Clock Control (复位和时钟控制)的缩写,它是STM32内部的一个重要外设,负责管理各种时钟源和时钟分频,以及为各个外设提供时钟使能。RCC模块可以通过寄存器操作或者库函数来配置。RCC是复位和时钟控制模块,它负责管理STM32内部的各种时钟源和时钟分频,以及为各个外设提供时钟使能。时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。不同的外

0. 写在最前

本栏目笔记都是基于stm32F10x

1. RCC简介

RCC是Reset and Clock Control (复位和时钟控制)的缩写,它是STM32内部的一个重要外设,负责管理各种时钟源和时钟分频,以及为各个外设提供时钟使能。RCC模块可以通过寄存器操作或者库函数来配置。

RCC是复位和时钟控制模块,它负责管理STM32内部的各种时钟源和时钟分频,以及为各个外设提供时钟使能。时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。不同的外设可能需要不同的时钟频率,所以RCC模块可以通过寄存器操作或者库函数来配置系统时钟和总线时钟。

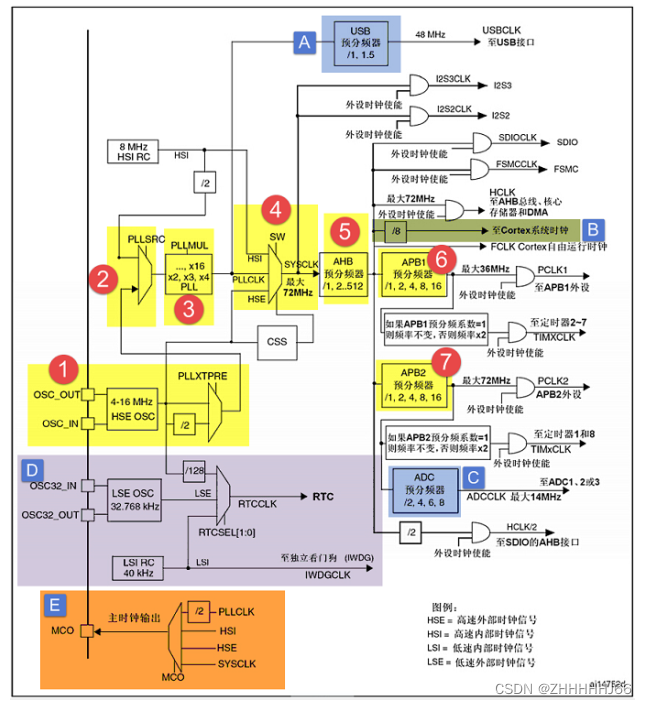

2. 时钟树介绍

主要元素介绍:

- HSE 高速外部时钟信号 :HSE 是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从 4-16MHZ 不等。当使用有源晶振时,时钟从 OSC_IN 引脚进入, OSC_OUT 引脚悬空,当选用无源晶振时,时钟从OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。

HSE 最常使用的就是 8M 的无源晶振。当确定 PLL 时钟来源的时候, HSE 可以不分频或者 2 分频,这个由时钟配置寄存器 CFGR 的位 17: PLLXTPRE 设置,我们设置为 HSE 不分频。 - PLL 时钟源:PLL 时钟来源可以有两个,一个来自 HSE,另外一个是 HSI/2,具体用哪个由时钟配置寄存器 CFGR 的位 16: PLLSRC 设置。HSI 是内部高速的时钟信号,频率为 8M,根据温度和环境的情况频率会有漂移,一般不作为 PLL 的时钟来源。这里我们选 HSE作为PLL的时钟来源。

- PLL 时钟 PLLCLK:通过设置 PLL 的倍频因子,可以对 PLL 的时钟来源进行倍频,倍频因子可以是:[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16],具体设置成多少,由时钟配置寄存器 CFGR的位 21-18: PLLMUL[3:0] 设置。我们这里设置为 9 倍频,因为上一步我们设置 PLL的时钟来源为 HSE=8M,所以经过 PLL 倍频之后的 PLL 时钟: PLLCLK = 8M *9 =72M。 72M 是 ST 官方推荐的稳定运行时钟,如果你想超频的话,增大倍频因子即可,最高为 128M。我们这里设置 PLL 时钟: PLLCLK = 8M *9 = 72M

- 系统时钟 SYSCLK:系统时钟来源可以是: HSI、 PLLCLK、 HSE,具体的时钟配置寄存器 CFGR 的位 1-0:SW[1:0] 设置。我们这里设置系统时钟: SYSCLK = PLLCLK = 72M。

- AHB 总线时钟 HCLK:系统时钟 SYSCLK 经过 AHB 预分频器分频之后得到时钟叫 APB 总线时钟,即 HCLK,分频因子可以是:[1,2,4, 8, 16, 64, 128, 256, 512],具体的由时钟配置寄存器 CFGR 的位7-4 : HPRE[3:0] 设置。片上大部分外设的时钟都是经过 HCLK 分频得到,至于 AHB总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里只需粗线条的设置好 APB 的时钟即可。我们这里设置为 1 分频,即 HCLK=SYSCLK=72M

- APB2 总线时钟 HCLK2:APB1 总线时钟 PCLK1 由 HCLK 经过低速 APB 预分频器得到,分频因子可以是:[1,2,4,

8, 16],具体的由时钟配置寄存器 CFGR 的位 10-8: PRRE1[2:0] 决定。 HCLK1 属于低速的总线时钟,最高为 36M,片上低速的外设就挂载到这条总线上,比如 USART2/3/4/5、SPI2/3, I2C1/2 等。至于 APB1 总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里只需粗线条的设置好 APB1 的时钟即可。我们这里设置为 2 分频,即 PCLK1 = HCLK/2 = 36M。

下图为newbing给我写的的系统时钟和总线时钟的关系框图(还不错):

+-----------------+ +-----------------+

| 内部RC振荡器 | | 外部晶振或信号源 |

| HSI/LSI | | HSE/LSE |

+-----------------+ +-----------------+

| |

+----------+----------+

|

v

+-----------+

| 时钟源选择 |

+-----------+

|

v

+-----------+

| 锁相环(PLL)|

+-----------+

|

v

+-----------+

| 系统时钟(SYSCLK)|

+-----------+

|

+---------+---------+---------+

v v v v

+-------+ +-------+ +-------+ +-------+

| AHB总线| | APB1总线| | APB2总线| | 外设时钟|

| HCLK | | PCLK1 | | PCLK2 | | TIMxCLK|

+-------+ +-------+ +-------+ +-------+

其他元素介绍:

**A:USB 时钟:**USB 时钟是由 PLLCLK 经过 USB 预分频器得到,分频因子可以是: [1,1.5],具体的由时钟配置寄存器 CFGR 的位 22: USBPRE 配置。 USB 的时钟最高是 48M,根据分频因子反推过来算, PLLCLK 只能是 48M 或者是 72M。一般我们设置 PLLCLK=72M,

USBCLK=48M。 USB 对时钟要求比较高,所以 PLLCLK 只能是由 HSE 倍频得到,不能使用 HSI 倍频

B:Cortex 系统时钟:Cortex 系统时钟由 HCLK 8 分频得到,等于 9M, Cortex 系统时钟用来驱动内核的系统定时器 SysTick, SysTick 一般用于操作系统的时钟节拍,也可以用做普通的定时

C:ADC 时钟:ADC 时钟由 PCLK2 经过 ADC 预分频器得到,分频因子可以是 [2,4,6,8],具体的由时钟配置寄存器 CFGR 的位 15-14: ADCPRE[1:0] 决定。很奇怪的是怎么没有 1 分频。ADC 时钟最高只能是 14M,如果采样周期设置成最短的 1.5 个周期的话, ADC 的转换时间可以达到最短的 1us。如果真要达到最短的转换时间 1us 的话,那 ADC 的时钟就得是 14M,反推 PCLK2 的时钟只能是: 28M、 56M、 84M、 112M,鉴于 PCLK2 最高是 72M,所以只能取 28M 和 56M

D:RTC 时钟、独立看门狗时钟:RTC 时钟可由 HSE/128 分频得到,也可由低速外部时钟信号 LSE 提供,频率为32.768KHZ,也可由低速内部时钟信号 HSI 提供,具体选用哪个时钟由备份域控制寄存器 BDCR 的位 9-8: RTCSEL[1:0] 配置。独立看门狗的时钟由 LSI 提供,且只能是由 LSI 提供, LSI 是低速的内部时钟信号,频率为 30~60KHZ 直接不等,一般取40KHZ

E:MCO 时钟输出:MCO 是 microcontroller clock output 的缩写,是微控制器时钟输出引脚,在 STM32 F1系列中由 PA8 复用所得,主要作用是可以对外提供时钟,相当于一个有源晶振。 MCO的时钟来源可以是: PLLCLK/2、 HSI、 HSE、 SYSCLK,具体选哪个由时钟配置寄存器CFGR 的位 26-24: MCO[2:0] 决定。除了对外提供时钟这个作用之外,我们还可以通过示波器监控 MCO 引脚的时钟输出来验证我们的系统时钟配置是否正确。

3. 官方的系统时钟初始化函数

tatic void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* 使能 HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* 等待HSE就绪并做超时处理 */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

// 如果HSE启动成功,程序则继续往下执行

if (HSEStatus == (uint32_t)0x01)

{

/* 使能预取指 */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK = 72M */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK = 72M */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK = 36M*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

/* 锁相环配置: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

/* 使能 PLL */

RCC->CR |= RCC_CR_PLLON;

/* 等待PLL稳定 */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* 选择PLLCLK作为系统时钟*/

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* 等待PLLCLK切换为系统时钟 */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /* 如果HSE 启动失败,用户可以在这里添加处理错误的代码 */

}

}

4. 配置时钟实验

4.1 使用HSE

一般情况下,我们都是使用 HSE,然后 HSE 经过 PLL 倍频之后作为系统时钟。通常的配置是:HSE=8M, PLL 的倍频因子为: 9,系统时钟就设置成:SYSCLK = 8M * 9 = 72M。使用 HSE,系统时钟 SYSCLK 最高是 128M。我们使用的库函数就是这么干的,当程序来到 main 函数之前,启动文件: statup_stm32f10x_hd.s 已经调用 SystemInit() 函数把系统时钟初始化成 72MHZ, SystemInit()在库文件: system_stm32f10x.c 中定义。如果我们想把系统时钟设置低一点或者超频的话,可以修改底层的库文件,但是为了维持库的完整性,我们可以根据时钟树的流程自行写一个

void HSE_SetSysClk( uint32_t RCC_PLLMul_x )

{

ErrorStatus HSEStatus;

// 把RCC 寄存器复位成复位值

RCC_DeInit();

// 使能 HSE

RCC_HSEConfig(RCC_HSE_ON);

HSEStatus = RCC_WaitForHSEStartUp();

if( HSEStatus == SUCCESS )

{

// 使能预取指

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

FLASH_SetLatency(FLASH_Latency_2);

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK1Config(RCC_HCLK_Div2);

RCC_PCLK2Config(RCC_HCLK_Div1);

// 配置 PLLCLK = HSE * RCC_PLLMul_x

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_x);

// 使能PLL

RCC_PLLCmd(ENABLE);

// 等待PLL稳定

while( RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET );

// 选择系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while( RCC_GetSYSCLKSource() != 0x08 );

}

else

{

/* 如果HSE 启动失败,用户可以在这里添加处理错误的代码 */

}

}

- 首先,调用RCC_DeInit()函数,把RCC寄存器复位成复位值,以便重新配置时钟系统。

- 然后,调用RCC_HSICmd(ENABLE)函数,使能HSI,并检查RCC->CR寄存器的HSIRDY位是否置1,表示HSI就绪。

- 如果HSI就绪,则继续配置时钟系统。首先,调用FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable)函数和FLASH_SetLatency(FLASH_Latency_2)函数,使能预取指缓冲区,并设置闪存延迟周期为2个时钟周期。这样可以提高闪存的读取速度和性能。

- 接着,调用RCC_HCLKConfig(RCC_SYSCLK_Div1)函数、RCC_PCLK1Config(RCC_HCLK_Div2)函数和RCC_PCLK2Config(RCC_HCLK_Div1)函数,分别设置AHB总线时钟(HCLK)、APB1总线时钟(PCLK1)和APB2总线时钟(PCLK2)的分频系数。在这里,HCLK = SYSCLK / 1 = SYSCLK;PCLK1 = HCLK / 2 = SYSCLK / 2;PCLK2 = HCLK / 1 = SYSCLK。

- 然后,调用RCC_PLLConfig(RCC_PLLSource_HSI_Div2, RCC_PLLMul_x)函数,配置PLL的时钟源为HSI/2,并设置PLL的倍频系数为RCC_PLLMul_x。在这里,PLL输入时钟为8MHz / 2 = 4MHz;PLL输出时钟为4MHz * RCC_PLLMul_x。

- 接着,调用RCC_PLLCmd(ENABLE)函数,使能PLL,并检查RCC->CR寄存器的PLLRDY位是否置1,表示PLL就绪。

- 最后,调用RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK)函数,选择系统时钟源为PLL输出时钟,并检查RCC->CFGR寄存器的SWS位是否等于0x08(二进制1000),表示系统时钟切换成功。

4.2 使用HIS

当 HSE 故障的时候,如果 PLL 的时钟来源是 HSE,那么当 HSE 故障的时候,不仅 HSE 不能使用,连 PLL 也会被关闭,这个时候系统会自动切换 HSI 作为系统时钟,此时 SYSCLK=HSI=8M,如果没有开启 CSS 和 CSS 中断的话,那么整个系统就只能在低速率运行,这是系统跟瘫痪没什么两样。如果开启了 CSS 功能的话,那么可以当 HSE 故障时,在 CSS 中断里面采取补救措施,使用 HSI,并把系统时钟设置为更高的频率,最高是 64M, 64M 的频率足够一般的外设使用,如:ADC、 SPI、 I2C 等。但是这里就又有一个问题了,原来 SYSCLK=72M,现在因为故障改成 64M,那么那些外设的时钟肯定被改变了,那么外设工作就会被打乱,那我们是不是在设置 HSI 时钟的时候,也重新调整外设总线的分频因子,即 AHB, APB2 和 APB1 的分频因子,使外设的时钟达到跟 HSE 没有故障之前一样。但是这个也不是最保障的办法,毕竟不能一直使用 HSI,所以当HSE 故障时还是要采取报警措施。还有一种情况是,有些用户不想用 HSE,想用 HSI,但是又不知道怎么用 HSI 来设置系统时钟,因为调用库函数都是使用 HSE,下面我们给出个使用 HSI 配置系统时钟例子,起个抛砖引玉的作用

void HSI_SetSysClk( uint32_t RCC_PLLMul_x )

{

__IO uint32_t HSIStatus = 0;

// 把RCC 寄存器复位成复位值

RCC_DeInit();

// 使能 HSI

RCC_HSICmd(ENABLE);

HSIStatus = RCC->CR & RCC_CR_HSIRDY;

if( HSIStatus == RCC_CR_HSIRDY )

{

// 使能预取指

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

FLASH_SetLatency(FLASH_Latency_2);

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK1Config(RCC_HCLK_Div2);

RCC_PCLK2Config(RCC_HCLK_Div1);

// 配置 PLLCLK = HSE * RCC_PLLMul_x

RCC_PLLConfig(RCC_PLLSource_HSI_Div2, RCC_PLLMul_x);

// 使能PLL

RCC_PLLCmd(ENABLE);

// 等待PLL稳定

while( RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET );

// 选择系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while( RCC_GetSYSCLKSource() != 0x08 );

}

else

{

/* 如果HSI 启动失败,用户可以在这里添加处理错误的代码 */

}

}

6. 写在最后

给个赞吧😄

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)