RJ45-以太网口PCB布局布线设计规范

我们常见的网口有百兆网口和千兆网口,他们的区别在于百兆网口只有两对差分,一对收,一对发,另外四根是备用的;千兆网口有四对差分,两对收,两对发,如图3所示,可以了解其对应的管脚定义。RJ45网口、变压器、PHY芯片及主芯片;还有一种RJ45与变压器进行了集成,分别如图1、图2所示;网口模块组成-RJ45与变压器未集成网口模块组成-RJ45与变压器集成三,网口模块的PCB设计布局注意事项1.1RJ45

一,以太网口概述

以太网(Ethernet)是一种计算机局域网组网技术,以太网是当前应用最普遍的局域网技术。Ethernet的接口是实质是MAC通过MII总线控制PHY的过程,以太网接口电路主要由MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成,目前常见的以太网接口芯片,如LXT971、RTL8019、RTL8201、、CS8900、DM9008 等,其内部结构也主要包含这两部分。一般32位处理器内部实际上已包含了以太网MAC控制,但并未提供物理层接口,因此,需外接一片物理层芯片以提供以太网的接入通道。

常用的单口10M/100Mbps 高速以太网物理层接口器件主要有 RTL8201、LXT971等,均提供MII接口和传统7线制网络接口,可方便的与CPU接口。以太网物理层接口器件主要功能一般包括:物理编码子层、物理媒体附件、双绞线物理媒体子层、10BASE-TX 编码/解码器和双绞线媒体访问单

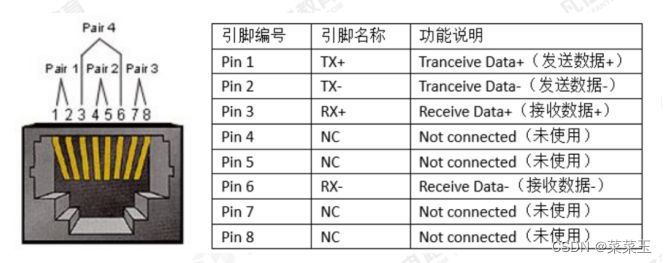

二,以太网的接口引脚定义,以及电路组成部分

我们常见的网口有百兆网口和千兆网口,他们的区别在于百兆网口只有两对差分,一对收,一对发,另外四根是备用的;千兆网口有四对差分,两对收,两对发,如图3所示,可以了解其对应的管脚定义。

网口模块的组成主要包括了:RJ45网口、变压器、PHY芯片及主芯片;还有一种RJ45与变压器进行了集成,分别如图1、图2所示;

网口模块组成-RJ45与变压器未集成

网口模块组成-RJ45与变压器集成

三,网口模块的PCB设计布局注意事项

1.1 RJ45和变压器之间的距离尽可能的短,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;以太网转换芯片和变压器之间的距离应尽可能短,一般不超过5inch。

1.2 复位电路信号应当尽可能的靠近以太网转换芯片,并且若可能的话应当远离TX、RX和时钟信号。

1.3 时钟电路应当尽可能的靠近以太网转换芯片,远离电路板边缘、其他高频信号、I/O端口、走线或磁性元件周围。总体布局要求,如图4所示。

四,网口模块的PCB设计布线注意事项

;网口的差分尽量走表底层,差分对之间的间距至少4W以上,由于管脚分布、过孔、以及走线空间等因素存在,使得差分线长度不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量,因此差分对内的等长约束为5mil,差分对之间不用进行等长,等长时注意符合差分等长规则,

;RJ45接口区域:内部所有层挖空处理。如图7所示,RJ45接口的G1,G2,G3和G4管脚的走线至少需要加粗至1mm以上,跨接电感和电容靠近接口放置,旁边多打地过孔

;RJ45接口区域:内部所有层挖空处理。如图7所示,RJ45接口的G1,G2,G3和G4管脚的走线至少需要加粗至1mm以上,跨接电感和电容靠近接口放置,旁边多打地过孔

接口挖空示意图

跨接电感走线示意图

变压器的处理

变压器所有层挖空(只挖一半,另一半铺铜处理,均匀的打上地过孔,建议间隔50mil一个),变压器到接口部分不用控阻抗,走线加粗处理;变压器到PHY芯片差分走线,控制100ohm差分阻抗。如图9所示。

变压器区域除差分信号外其他信号

走线都加粗到20mil以上,变压器地网络的回流通过粗线连接起来。

以太网转换芯片的处理

以太网转换芯片的处理

以太网芯片到CPU的RGMII接口线的发送部分和接收部分要分开布线,不要将接收和发送网络混合布线,线与线之间需要满足3W,发送和接收总线分别进行等长,等长范围100mil

25M晶振下面不能走其他信号线,时钟线不用走在RJ45座子下面,复位信号的布线满足3W要求。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)