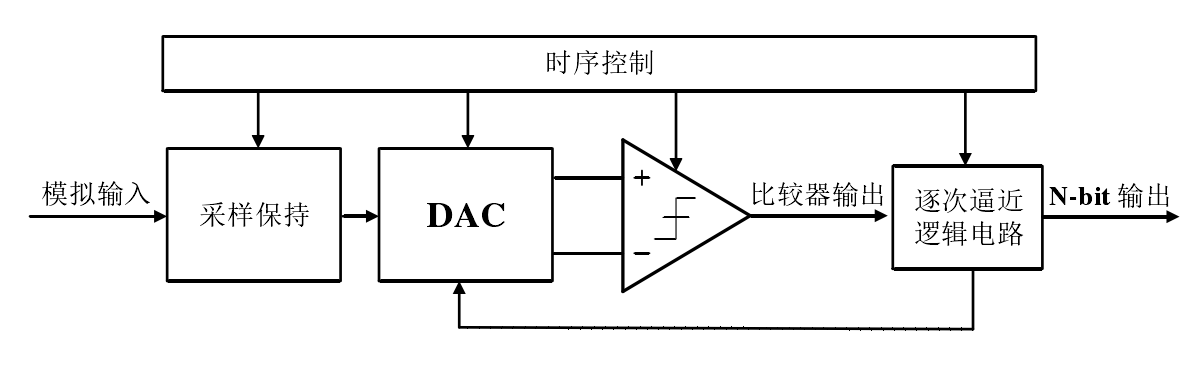

SAR ADC单位电容确定

好久没写点东西了,恰好之前做出来了的16位SAR ADC,现在回过来来回顾一下之前学习的知识,这次是SAR ADC单位电容取值的确定,其实主要由以下几个方面来考虑,结合一下蒙卡仿真即可

好久没写点东西了,恰好之前做出来了的16位SAR ADC,现在回过来来回顾一下之前学习的知识,这次是SAR ADC单位电容取值的确定,其实主要由以下几个方面来考虑,结合一下蒙卡仿真即可:

1、KT/C噪声的影响:

量化噪声是数据转换器的基本限制因素,另一个不可避免的限制是KT/C噪声,它出现在所有实际的采样数据系统中,因为它的产生是由于不可避免的、与采样开关相关的热噪声。当 KT/C 噪声电压等于量化噪声电压时,总的噪声功率将扩大一倍,信噪比降低 3dB,有效位数减少 1/2 位,所以要求采样电路的 KT/C 噪声功率要小于量化噪声功率。对于差分结构电路,在进行差分采样时,两端都会产生热噪声,且两端的采样电容值是相等的,因此为2KT/C。

对于总采样电容的计算,在工业界中通常存在一种从动态 SNR 的角度来决定电容的选择,即总噪声2KT/必须小于四分之一(或者更小)的量化噪声。这里采用工业标准来进行计算,有:

以2.5V为参考电压的12位全差分SAR ADC,对应的LSB约为1.2207mV。其中K代表玻尔兹曼常数,1.380649∗ 10−23J/K;T 代表室温,300K,可得:

可得Cu>0.03256fF,电容大小的选取一般都能满足热噪声的要求。

2、导通电阻的影响

输入信号的采样精度决定于采样保持电路的信号建立时间,而信号建立时间是采样开关管的导通电阻Ron与电容阵列DAC总采样电容Cs 的乘积。对于一般的采样电路输出电压与输入信号电压的关系可以表示为下式:

采样误差可以表示位输入信号电压与输出电压之差,如下式

为了保证 ADC 精度,采样误差必须小于 0.5 LSB。当输入信号等于Vref 时,会出现最大采样误差,即要求:

可得到采样开关导通电阻的要求如下式:

在式中,Ts 为采样周期,τ为时间常数,Cs采为对应的采样电容值,N=12。可以看出,在设计开关网络时,要注意的一个问题就是对应不同的采样电容,它所对应的 Ron也不一样。为了使每条支路的时间常数均相等,有相同的建立精度,电容增大的同时,开关的导通电阻应等比例的减小,即开关管的尺寸应与对应电容同比例缩放。

3、电容失配的影响:

相对于热噪声而言,在电路结构中,单位电容的失配成了限制电容阵列线性度的最主要因素,根据开关切换方式的不同,电容失配对整体结构的影响也会不同。有文献对三种开关切换方式进行了总结,并求出了每一种切换方式对应线性度的分析。这里直接引用该文献得到的Vcm_based切换方式线性度分析的结果。对于这种切换方式,差分电路结构的最大 DNL 和 INL 的标准差为:

在设计中,为了保证精度足够,根据正态分布的 3 定律,要求最大非线性度的3倍小于 LSB /2,可得:

代入N=12,可得电容的失配率要求小于 0.561%。

是单位电容标准差,可通过蒙特卡洛仿真得到。根据单位电容所采用的工艺类型,单位电容计算得到大小为198.1264fF,满足热噪声对总电容的要求。

其 500次蒙特卡洛仿真结果如图所示:

由蒙特卡洛仿真结果可知:

-

电容失配呈正态分布;

-

单位电容容值为198.1264fF,均值为196.488fF,1 个标准偏差为 45.61aF,失配率为 0.0232%;3个标准差失配率为0.0696%,满足电容失配率要求。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)