整理笔记——上拉电阻、下拉电阻

百度百科上的解释:上拉就是将不确定的信号通过一个电阻钳位在,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在。上拉是对器件输入电流,下拉是输出电流;强弱只是上拉电阻的阻值不同,没有什么严格区分;对于非(或漏极)输出型电路(如普通)提供电流和电压的能力是有限的,上拉电阻的功能主要是为输出型电路输出电流通道。乍一看不是通俗易懂啊,下面是我简单的理解。

百度百科上的解释:

上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平。

上拉是对器件输入电流,下拉是输出电流;强弱只是上拉电阻的阻值不同,没有什么严格区分;对于非集电极(或漏极)开路输出型电路(如普通门电路)提供电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

乍一看不是通俗易懂啊,下面是我简单的理解。

一、上拉电阻

上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。上拉电阻可以提高电路驱动能力。

1.1 上拉电阻提高电路驱动能力

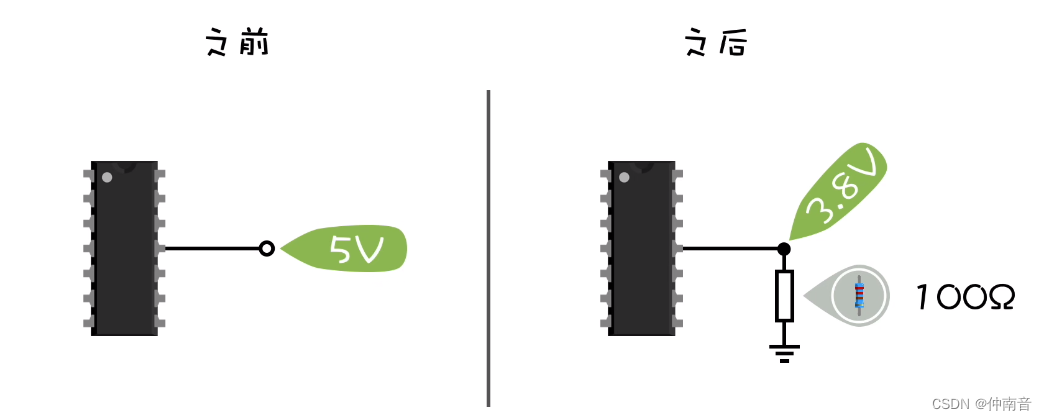

MCU使用5V供电,当IO口输出高电平,其内部电路为接5V的mos管导通,接地的mos管截止看做无穷大电阻,因此IO引脚上的电压就是MCU供电的5V电压。

当MCU的IO引脚接负载(这里用100R电阻代替)时,引脚上的电压只有3.8V,电压为什么变了:

这就要看MCU内部构造了,因为MCU内部电源是有内阻的,再加上接5V的mos管导通也有一定的阻值,电路等效一下就是5V电源串联两个电阻接地,电压自然就被拉低了。

接上拉电阻后该点的电压情况:(提高了电路的驱动能力)

再从MCU内部构造分析,MCU引脚上接上拉电阻以后,等效电路图如下,其相当于再MCU的内阻上并联了一个电阻,从而减小了内阻上的电流,因此引脚的驱动能力被提高了。

1.2 上拉电阻将不确定的信号钳位高电平

为什么会有不确定的信号呢?比如当引脚处于开漏输出时,想让引脚输出高电平,则需要将上面的mos断开,下面的mos截止,这样就相当于这个引脚连接着两个无穷大的电阻,这两个电阻就相当于断开,所以此时IO的引脚状态是不确定的。

当接了10K上拉电阻后,电路上面的一个无穷大的电阻与10k电阻并联后,总阻值越为10k左右,此时5V电压几乎全加在了下面的无穷大电阻上,因此引脚上输出了高电平。

二、下拉电阻

下拉电阻可以将不确定的信号通过一个电阻钳位在低电平。

当MCU的IO引脚处于数字输入模式时,内部实际是一个触发器,这里用电阻+三极管代替,方便理解。

IO引脚输入之所以是不确定的,是因为P型三极管的的集电极与基级的两块半导体之间的阻值太大,类似断开,因此P型半导体上的电压是飘忽不定的,对应IO引脚上的电压也一个不确定的信号。

接下拉电阻后,IO引脚上为确定的低电平,因为下拉电阻与三极管是串联关系,三极管认为是无穷大电阻,5V电压全部加在了三极管上,所以下拉电阻上几乎没有电压,IO引脚输入也是一个确定的低电平信号。

当再引脚上输入高电平时,下拉电阻有巧妙的将点位设置为高电平。

总结:对于MCU来说,

上拉电阻用在MCU的IO输出情况下,

下拉电阻用在MCU的IO输入情况下。

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)