(十七) 基于cadence 617 电流镜负载差分放大器的设计

基于Allen 的CMOS模拟集成电路设计英文版P216电路

电流镜负载差分放大器的设计

文章目录

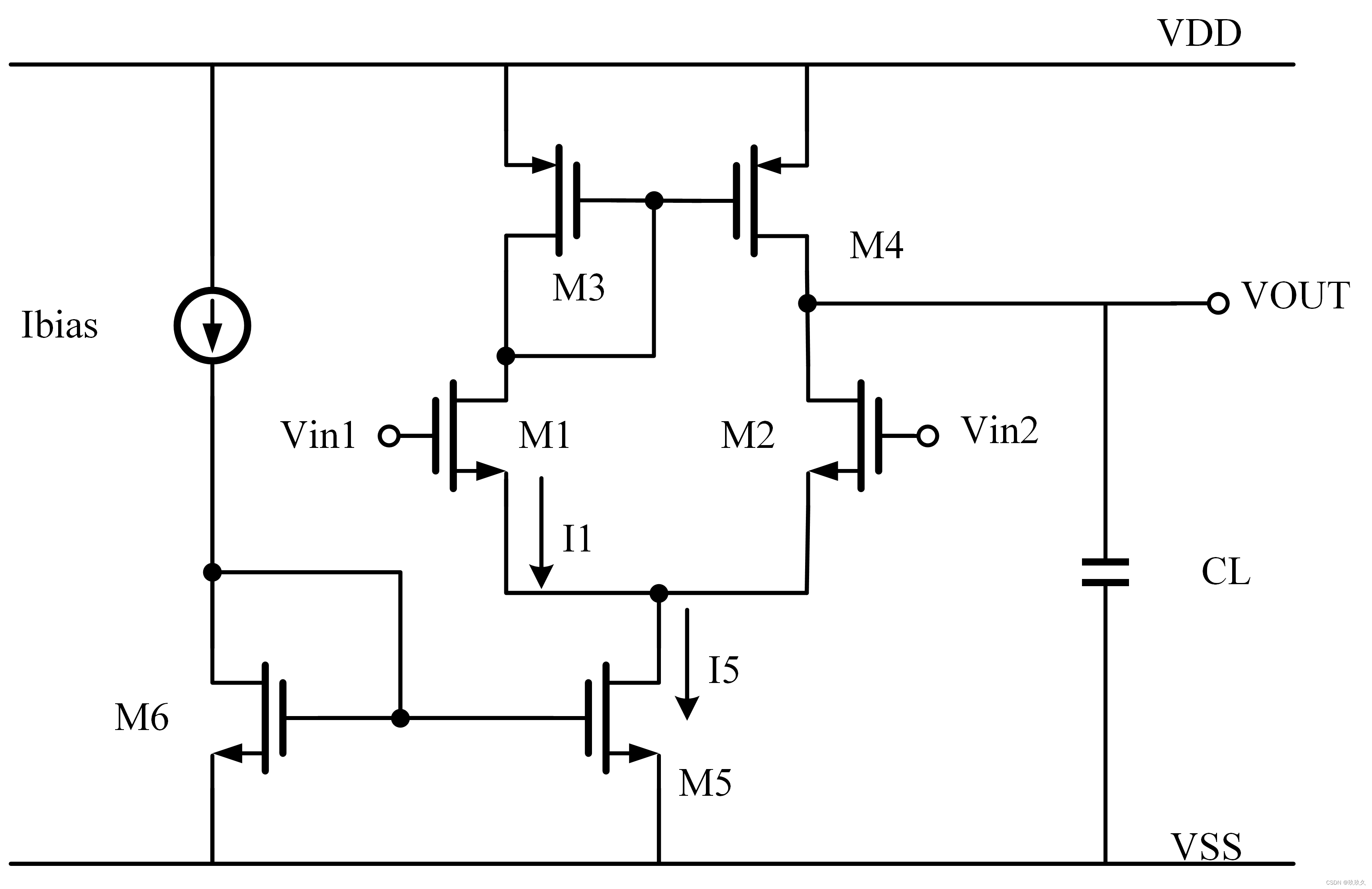

一、原理图

二、设计指标

| VDD | 2.5 V |

|---|---|

| VSS | -2.5 v |

| SR | ≥ 10 V/us |

| f-3dB | ≥ 100 kHz(CL= 5 pf) |

| AV | ≤ 1mW |

| ICMR | -1.5 ≤ ICMR ≤ 2 V |

| pdiss | ≤ 1mW |

三、指标分析

3.1 压摆率 SR

压摆率是指:当大信号情况下运放的输入端接入大的阶跃信号,造成输出信号波形变化,其变化对时间的比值。单位:V/us

S

R

=

I

S

S

C

L

SR = \frac {I_{SS}}{C_{L}}

SR=CLISS

3.2 放大倍数

A v = g m 1 R o u t A_{v} =g_{m 1} R_{\mathrm{out}} Av=gm1Rout

3.3 -3dB频率

ω − 3 d B = 1 R o u t C L \\\omega_{-3 \mathrm{~dB}} =\frac{1}{R_{\mathrm{out}} C_{L}} ω−3 dB=RoutCL1

3.4 输入共模范围

V I C ( max ) = V D D − V S G 3 + V T N 1 V I C ( min ) = V D S 5 ( s a t ) + V G S 1 = V D S 5 ( s a t ) + V G S 2 \\V_{I C}(\max ) =V_{D D}-V_{S G 3}+V_{T N 1} \\V_{I C}(\min ) =V_{D S 5}(\mathrm{sat})+V_{G S 1}=V_{D S 5}(\mathrm{sat})+V_{G S 2} VIC(max)=VDD−VSG3+VTN1VIC(min)=VDS5(sat)+VGS1=VDS5(sat)+VGS2

3.5 功耗

P d i s s = ( V D D + ∣ V S S ∣ ) ( I 5 ) = ( V D D + ∣ V S S ∣ ) ( I 3 + I 4 ) \\P_{\mathrm{diss}} =\left(V_{D D}+\left|V_{S S}\right|\right)\left(I_{5}\right)=\left(V_{D D}+\left|V_{S S}\right|\right)\left(I_{3}+I_{4}\right) Pdiss=(VDD+∣VSS∣)(I5)=(VDD+∣VSS∣)(I3+I4)

四、条件约束

- 在已知功耗Pdiss或者CL 的前提下选择 I5 来满足 SR

- 看看Rout 是否满足频率响应

- 设计( W/L)3.4来满足ICRR的上限

- 设计( W/L)1.2来满足放大倍数AV

- 设计( W/L)5来满足ICRR的下限

五、设计流程

已知参数:

| N | P | |

|---|---|---|

| λn | 0.035 V^-1 | 0.046 V^-1 |

| VTH | 0.7 V | 0.6 V |

| K | 13.93 × 10-5 A/V^2 | 4.31 × 10-5 A/V^2 |

1)由压摆率要求得:I5 ≥ 50u 结合功耗要求 I5 ≤ 200 u 即 50u ≤ I5 ≤ 200u

2)带宽与 ROUT 有关要求 ROUT = 318 K

R

O

U

T

=

2

I

5

(

λ

p

+

λ

n

)

≤

318

K

\begin{aligned} R_{OUT} =\frac{2}{I_{5}\left(\lambda_{p}+\lambda_{n}\right)} ≤318K \end{aligned}

ROUT=I5(λp+λn)2≤318K

由此可以定出 I5 ≥ 78 u

3)最大输入共模电压为

V

S

G

3

=

V

D

D

−

V

I

C

(

max

)

+

V

T

N

1

=

2.5

−

2

+

0.7

=

1.2

V

\begin{aligned}V_{S G 3} & =V_{D D}-V_{I C}(\max )+V_{T N 1}\\ & =2.5 - 2+ 0.7\\ & = 1.2V\end{aligned}

VSG3=VDD−VIC(max)+VTN1=2.5−2+0.7=1.2V

则

V

S

G

3

=

1.2

V

=

2

⋅

50

μ

A

(

43

μ

A

/

V

2

)

(

W

3

/

L

3

)

+

0.5

⟹

W

3

/

L

3

=

W

4

/

L

4

=

4.7

V_{S G 3}=1.2 \mathrm{~V}=\sqrt{\frac{2 \cdot 50 \mu \mathrm{A}}{\left(43 \mu \mathrm{A} / \mathrm{V}^{2}\right)\left(W_{3} / L_{3}\right)}}+0.5\\ \Longrightarrow W_{3} / L_{3}=W_{4} / L_{4}= 4.7

VSG3=1.2 V=(43μA/V2)(W3/L3)2⋅50μA+0.5⟹W3/L3=W4/L4=4.7

4)小信号指标可得

100

V

/

V

=

g

m

1

R

out

=

g

m

1

g

d

s

2

+

g

d

s

4

=

(

2

⋅

139

μ

A

/

V

2

)

(

W

1

/

L

1

)

(

0.046

+

0.035

)

50

μ

A

=

29.11

(

W

1

/

L

1

⟹

W

1

/

L

1

=

W

2

/

L

2

=

11.8

100 \mathrm{~V} / \mathrm{V}=g_{m 1} R_{\text {out }}=\frac{g_{m 1}}{g_{d s 2}+g_{d s 4}}=\frac{\sqrt{\left(2 \cdot 139 \mu \mathrm{A} / \mathrm{V}^{2}\right)\left(W_{1} / L_{1}\right)}}{(0.046+0.035) \sqrt{50 \mu \mathrm{A}}}=29.11\sqrt{(W_{1} / L_{1}}\\ \Longrightarrow W_{1} / L_{1}=W_{2} / L_{2}= 11.8

100 V/V=gm1Rout =gds2+gds4gm1=(0.046+0.035)50μA(2⋅139μA/V2)(W1/L1)=29.11(W1/L1⟹W1/L1=W2/L2=11.8

5) 最小输入共模电压得出

V

D

S

5

=

V

I

C

(

min

)

+

V

G

S

1

−

V

S

S

=

−

1.5

+

2.5

−

2

⋅

50

μ

A

(

139

μ

A

/

V

2

)

(

11.8

)

−

0.7

=

0.05

V

\begin{aligned}V_{D S 5} & =V_{I C}(\min )+V_{G S 1}-V_{SS}\\ & =-1.5 + 2.5-\sqrt{\frac{2 \cdot 50 \mu \mathrm{A}}{\left(139 \mu \mathrm{A} / \mathrm{V}^{2}\right)\left(11.8\right)}}- 0.7\\ & =0.05V \end{aligned}

VDS5=VIC(min)+VGS1−VSS=−1.5+2.5−(139μA/V2)(11.8)2⋅50μA−0.7=0.05V

则

W

5

L

5

=

2

I

5

K

N

′

V

D

S

(

s

a

t

)

2

=

255

\frac{W_{5}}{L_{5}}=\frac{2 I_{5}}{K_{N}^{\prime} V_{D S}(\mathrm{sat})^{2}}=255

L5W5=KN′VDS(sat)22I5=255

考虑到宽长比太大,现增加(W/L)1,也可以增大AV

(

W

1

/

L

1

)

=

20

⟹

W

5

/

L

5

=

59

(W_{1} / L_{1})=20\Longrightarrow W_{5} / L_{5}= 59

(W1/L1)=20⟹W5/L5=59

汇总为表

| W/L | I | |

|---|---|---|

| M1、M2 | 20 | 50u |

| M3、M4 | 4.7 | 50u |

| M5 | 59 | 100u |

六、仿真

6.1 共模范围仿真

仿真结果

可以看出output swing 随共模电压的增加而降低

当输入共模信号为 -1.55V 直流工作点正常

为什么I1、I2的和不等于I5 ? 因为B端漏电,B端电位为0,而VS为负电压,则寄生二极管将会导通

将输入管的SB相接,漏电现象消失了

当输入共模信号为 2V 直流工作点正常

M5管子的VDS很大,由于沟道调制效应,复制电流会变大

6.2 Stb仿真

输入Vin1=-1.55 V

仿真结果 f-3dB带宽满足要求,后可以考虑增加f-3dB

6.3 压摆率仿真

七、Improve

7.1 -3dB频率怎么改善?

从公式中可知:要提高 ω -3dB 则需要减小 ROUT 进而增加电流 I

ω

−

3

d

B

=

1

R

o

u

t

C

L

R

O

U

T

=

2

I

5

(

λ

p

+

λ

n

)

\\\omega_{-3 \mathrm{~dB}} =\frac{1}{R_{\mathrm{out}} C_{L}}\\ \begin{aligned} R_{OUT} =\frac{2}{I_{5}\left(\lambda_{p}+\lambda_{n}\right)} \end{aligned}

ω−3 dB=RoutCL1ROUT=I5(λp+λn)2

增加电流会产生什么影响呢?

第一:功耗会增加 (P = I U)

第二:造成input swing 降低 (VGSVOV增加)

电流增加到110u

造成增益降低的原因是: 电流的增加 会使得VOV 增加

A

v

=

g

m

⋅

R

o

u

t

=

2

I

D

V

O

V

⋅

1

(

λ

n

+

λ

p

)

⋅

I

D

=

2

V

O

V

(

λ

n

+

λ

p

)

V

O

V

=

V

G

S

−

V

T

H

=

2

I

D

μ

n

C

o

x

W

L

′

A_{v}=g_{m} \cdot \operatorname{R_{out}}=\frac{2 I_{D}}{V_{O V}} \cdot \frac{1}{\left(\lambda_{n}+\lambda_{p}\right) \cdot I_{D}}=\frac{2}{\operatorname{V_{OV}}\left(\lambda_{n}+\lambda_{p}\right)}\\ V_{O V}=V_{G S}- V_{T H}=\sqrt{\frac{2 I_{D}}{\mu_{n} C_{o x} \frac{W}{L^{\prime}}}}

Av=gm⋅Rout=VOV2ID⋅(λn+λp)⋅ID1=VOV(λn+λp)2VOV=VGS−VTH=μnCoxL′W2ID

f -3dB增加的原因是: 电流增加造成ROUT下降

八、基本指标仿真

1. 1 共模输入范围(ICMR)

用该结构仿真得到的线性范围同时受到输入共模范围和输出摆幅的限制,因此无法用该结构精确测得ICMR。对于一般的运放,输出摆幅范围通常大于输入共模范围,故该方法能够大致预估输入共模范围

仿真结果:共模范围基本符合

为什么斜率小一点点应该问题不大吧

1.2 输出摆幅(SW)仿真

下图所示的反相电压放大器增益为-10。将运放的供电电源改成 ± 0.5VDD,正输入端接 0 电位,从而给运放提供一个位于电源轨中间的共模输入电平,在此基础上仿真输出电压摆幅。在如图 1-3(b)所示的 DC 扫描曲线上的线性部分即为该供电条件下的输出电压摆幅 ,在此基础上整体加上 0.5VDD 即为单电源供电时的输出电压摆幅

结果:输出范围 -488 ~ 496m

1.3 输入失调电压(VOS)仿真

VOS= 4.7m,也可以扫描输入看整个共模范围变化时候的VOS 的变化

总结

基于Allen 的CMOS模拟集成电路设计来简单验证电路

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献11条内容

已为社区贡献11条内容

所有评论(0)