Quartus II连接开发板后从绘图、分配管脚、编译到下载的过程

本文介绍的是Quartus II在连接DE0开发板后从绘图、分配管脚、编译到下载的过程,还包括Verilog 代码生成symbol部分。

前言

本文介绍的是Quartus II在连接DE0开发板后从绘图、分配管脚、编译到下载的过程,还包括Verilog 代码生成symbol部分。

一、开发板的连接与测试

将开发板的电源线和USB串口分别接在插线板和电脑主机上,打开开发板的开关,然后在设备管理器——>通用串行总线控制器这里找到USB-Blaster,右键,更新驱动设备——>浏览我的电脑以查找驱动设备。

找到Quartus II软件的安装位置,找到/drivers/这级目录后确定,等待驱动安装完成。

打开Quartus II软件,依照图片标出的顺序选择USB-Blaster[USB-0]。

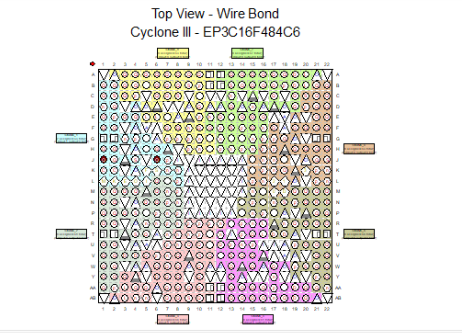

然后按Auto Detect键,检测出了EP3C16,这样就连接成功了,后面程序编译通过后直接下载就行了。

二、Quartus II下的操作

建工程、绘图等详细步骤可参见:Quartus II从建工程、绘图、编译到仿真详细过程。

下面的这个例子为:一个特定的开关控制一个特定LED灯的亮灭。

1.绘图

File——>New后选择Block Diagram/Schematic File新建框图并绘制如下。

2.分配管脚

在Assignments——>Pin Planner下依照DE0开发板的用户手册依次对自己用到的管脚进行添加。

3.参数设置

在Assignments——>Device…下按照下图中的标号依次设置参数,将不用的管脚置为“As input tri-stated”。

4.编译

编译后的bdf文件就看到了分配的管脚了。

5.下载到开发板

上面开发板的连接与测试通过之后,直接点击Start 按键,等待Progress进度条到达100%后就下载成功了。

6.开发板结果展示

来看看程序下载进去之后开发板的结果吧!

这个例子就是上图中的开关0控制LED0的亮灭,可以看到,开关打开后,LED0这个灯就亮了,所以我们的程序下载进了开发板并成功运行了。

三、Verilog 代码生成Symbol

创建Verilog HDL文件,写好代码后确保没有错误,不用编译代码。直接右击文件,选择Create Symbol Files for Current File,等待生成Symbol即可。

这里以2-4译码器为例,其Verilog代码如下:

module dec_2to4(IN,OUT);

input [2-1:0] IN;

output [4-1:0] OUT;

reg [4-1:0] OUT;

always @ (IN) begin

case(IN)

2'b00:OUT = 4'b0001;

2'b01:OUT = 4'b0010;

2'b10:OUT = 4'b0100;

2'b11:OUT = 4'b1000;

endcase

end

endmodule

按上面的方法生成Symbol后,在bdf文件空白处双击,在Project下就可以看到刚才生成的Symbol了。点击OK就可以将Symbol添加到bdf文件中了。

生成Symbol的功能就是你代码中所描述的功能。

总结

以上就是Quartus II在连接DE0开发板后从绘图、分配管脚、编译到下载的过程以及Verilog 代码生成symbol部分,这是很基础的操作,必须得熟练的掌握!

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)