ESD放电模式以及电源箝位 (power clamp )电路

由于ESD电压具有很快的上升速度(其ESD脉冲上升时间约在10ns左右),Vrc端的电压因为RC延迟效应无法跟得上VDD端的ESD电压上升速度,Vrc端的为低电位导致反相器工由于ESD电压具有很快的上升速度(其ESD脉冲上升时间约在10ns左右),Vrc端的电压因为RC延迟效应无法跟得上VDD端的ESD电压上升速度,Vrc端的为低电位导致反相器工作将输出端Vout电压上拉到高电位。从而Vg端的高电

目录

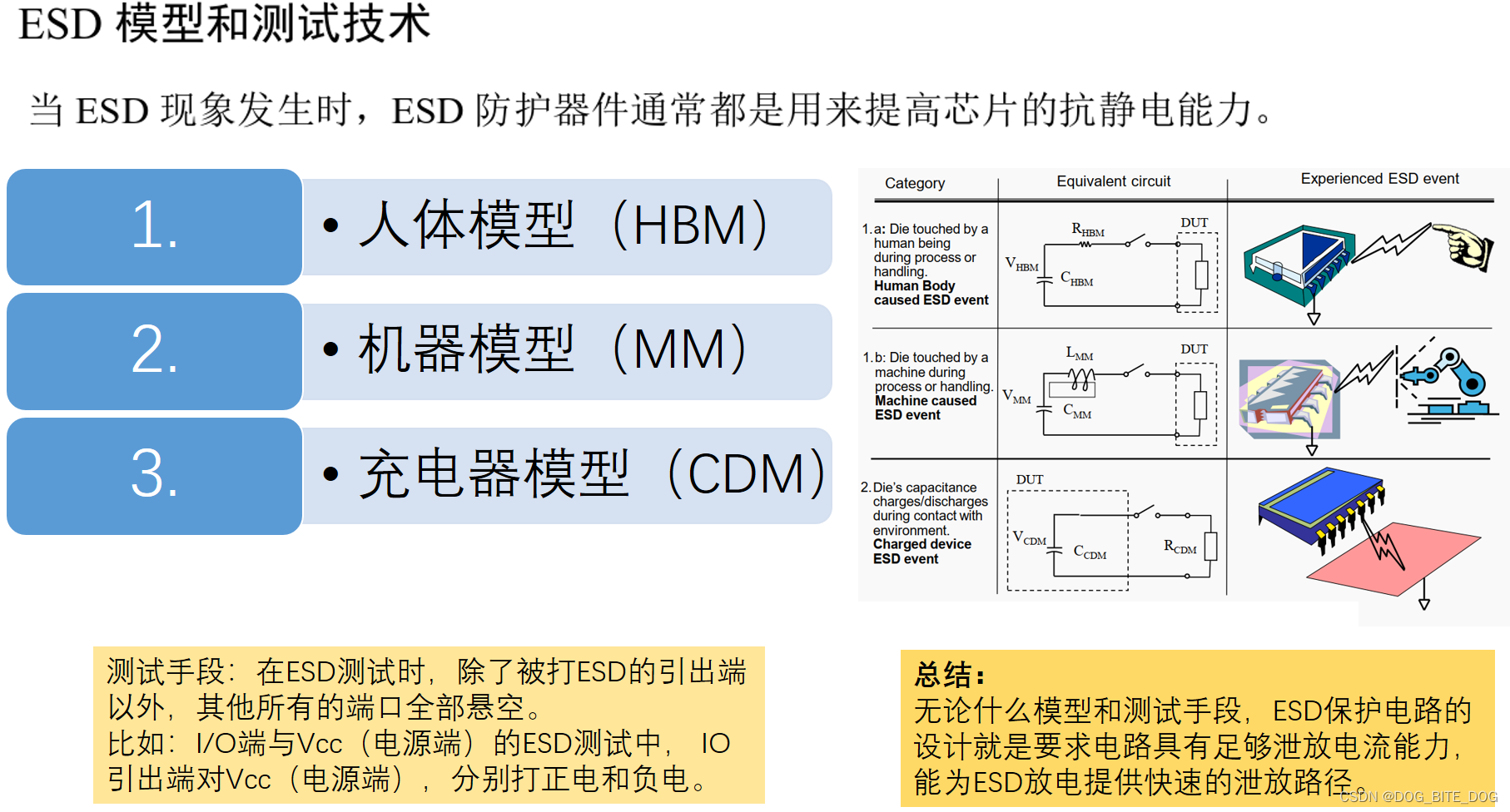

1.ESD的基本概念

2.ESD放电模式与泄放路径

2.1 I/O端与 Vcc或者 I/O端与 Vss

2.2 I/O端与 I/O端

2.3 Vcc(电源端)与Vss(地端)

2.4不同类型电压源

上图2-12中所示ESD防护网络仅适合等电压的多电源域之间使用,对于不等电压的多电源域,采用单个背靠背二极管的防护器件显然是行不通的,若两电源域的电压差大于0.7V,就会造成芯片在正常工作时电源域之间发生短路而严重损坏芯片。此时,可以采用串联多个二极管的方式来提高界面ESD器件的触发电压,当其触发电压高于被保护的电源域的电压差后,便不会引起电源域之间的短路行为,从而实现有效的ESD防护。但此时又需额外注意,多个二极管串联会使得器件的导通电阻也大大上升,这将严重恶化处于不同电源域的引脚间ESD通路的电压钳制性能,这一点在ESD设计时一定要额外考虑。

不同类型地与之相同

3. 电源箝位 (power clamp )电路

前面的叙述中可以看出电源箝位 (power clamp )在全芯片ESD保护电路设计中的重要性。可以说五种情况的ESD测试下泄放路径几乎都会包含该电路,电源钳位单元可以采用主泄放器件,RC+bigMOS组成的RCpowerclamp,或者RC+SCR组成的RCSCR钳位单元,SCR(Silicon Controlled Rectifier),硅控整流器,也叫晶闸管。

大多使用的是二极管和RCpowerclamp为组合的方法,这种结构复杂度小,稳定性高。

下图为典型RC触发的ESD钳位电路。也有一些厂商,直接提供了相应的symbol。

由于ESD电压具有很快的上升速度(其ESD脉冲上升时间约在10ns左右),Vrc端的电压因为RC延迟效应无法跟得上VDD端的ESD电压上升速度,Vrc端的为低电位导致反相器工作将输出端Vg电压上拉到高电位。从而Vg端的高电位触发导通了NMOS元件(Mesd)的晶体管,因而ESD电流便经由Mesd而泄放掉。由于晶体管Mesd的栅极导通电压约0.7V,所以Vg端要能够提供一大于0.7V的电压,且长达200ns 来导通Mesd元件的晶体管。这可由适当设计的电阻R,电容C,以及反相器内的晶体管尺寸来达成。

电路正常工作时:当芯片运行时,VDD的电压也是从0V逐渐上升到5V的,在power-on状态中,为了不影响内部电路的正常工作,Mesd元件需要保持在关闭状态,可通过设置RC时间常数来达到这一目的。因为VDD power-on的电压上升时间是约1ms 左右,而ESD电压的上升时间是在约10ns,所以把ESD侦测电路的RC时间常数设在0.1~1us,即可区分ESD事件来临和电路正常工作的两种工作状态。

4.全芯片ESD保护电路系统框图

项目中常见的全芯片ESD保护电路系统框图,基本上囊括了以上所说的所有ESD保护措施。

参考文献:

1.基于0.6_μm_CMOS工艺下的全芯片ESD防护研究_邹柯鹏

2.基于0.6μm_CMOS工艺ESD全芯片保护研究_何刚

3.基于0.18μm_CMOS工艺的全芯片ESD保护的研究_成辉

4.基于CMOS工艺的ESD器件及全芯片防护设计_郑亦菲

5.基于CMOS工艺的全芯片ESD保护电路设计_向洵

开放原子开发者工作坊旨在鼓励更多人参与开源活动,与志同道合的开发者们相互交流开发经验、分享开发心得、获取前沿技术趋势。工作坊有多种形式的开发者活动,如meetup、训练营等,主打技术交流,干货满满,真诚地邀请各位开发者共同参与!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)