UDP协议及verilog实现——(三)github项目阅读

开源代码的阅读和移植能力还是挺重要的,能帮助工程师快速的借助前人的基础完善自己的项目,在他人的基础上拓展自己的业务。

开源代码的阅读和移植能力还是挺重要的,能帮助工程师快速的借助前人的基础完善自己的项目,在他人的基础上拓展自己的业务。

一、GITHUB代码下载

UDP通信的verilog实现以下面的链接为基础进行:

GitHub - alexforencich/verilog-ethernet: Verilog Ethernet components for FPGA implementation

1.首先,百度一下,找到该代码所在网址。

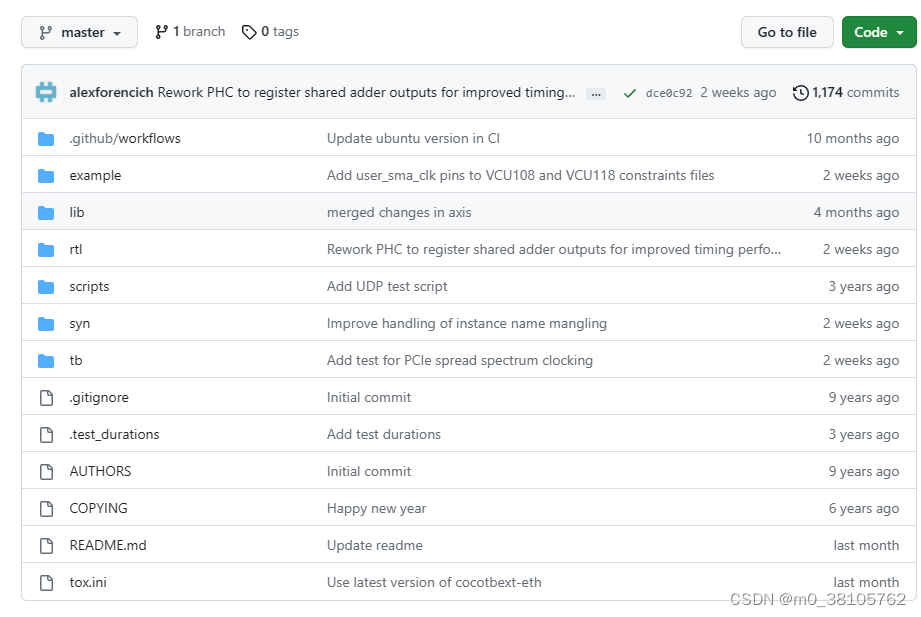

2.打开链接,大致看看内容,和readme。

可以看到,有example ,lib ,rtl ,scipts(for test),说明基本靠谱,比较完善了。可以直接下载到本地。

可以看到,有example ,lib ,rtl ,scipts(for test),说明基本靠谱,比较完善了。可以直接下载到本地。

二、代码框架分析

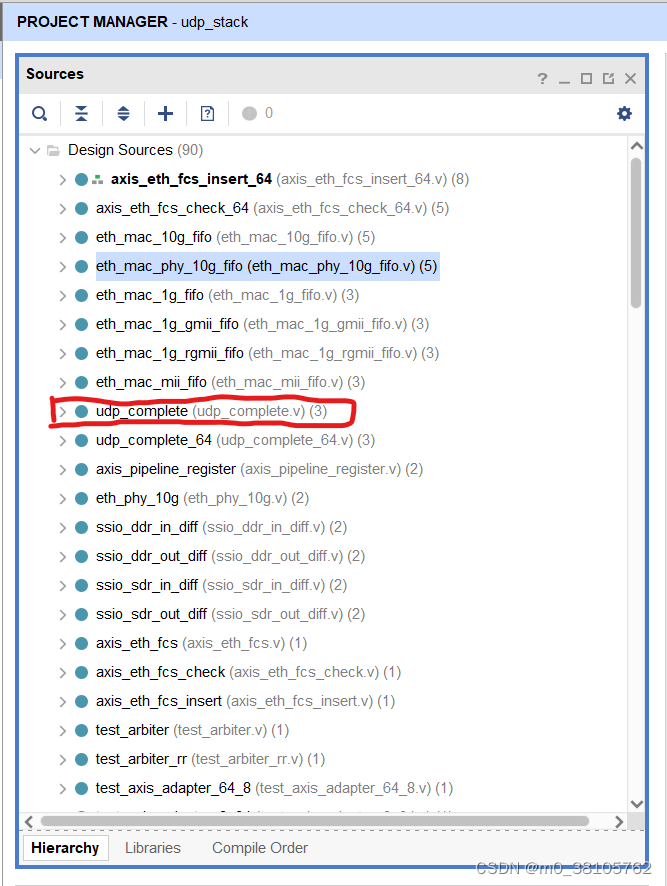

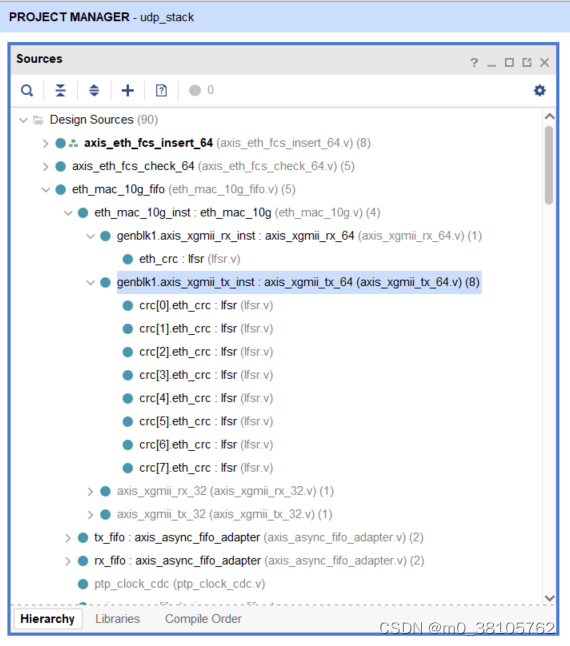

为了方便查看代码间关系,可以直接全部代码一股脑导到一个工程下,如下图。可以看到很多顶层,不过根据名称也能大致分辨功能,其中udp_complete就是udp协议栈的顶层模块。

接下去就是搭仿真环境或者硬肝了。。。硬肝推荐结合VSCODE和VIVADO一起看,VIVADO梳理层次,VSCODE看具体代码细节。

这里可以简单说下大致结构:

1.ip_arb_mux:这模块主要是支持多路IP数据流输入,做仲裁,单路情况下其实不需要该模块。

2.ip_complete:实现IP+ARP协议。其实就是完成1、UDP通信下的IP首部组包/解包和数据长度计算;2、ARP通过IP获取MAC以及根据ip回应mac;

3.udp:实现UDP首部打包/解包和crc计算;

其实不是很理解设计者的目的,udp_complete的顶层接口从ETH_IN/IP_IN/UDP_IN到ETH_OUT/IP_OUT/UDP_OUT有三对输入输出。其实按常规用法,UDP_IN->ETH_OUT就行了。

三、代码数据流分析——UDP/IP层封装

内部数据流向大致是udp_ip_tx->ip_eth_tx->eth_arb_mux

可以看出大致的命名规则和层次逻辑:

顶层 udp_complete/ip_complete,内部模块名称暗含了连接关系:

比如:udp中的udp_ip_tx,说明该模块是udp发送模块,实现udp层协议封装,输出是IP格式,应该接ip_tx模块;

而ip_eth_tx,说明该模块是IP发送模块,完成IP层协议封装,输出是ETH格式,应该接ETH_TX模块。

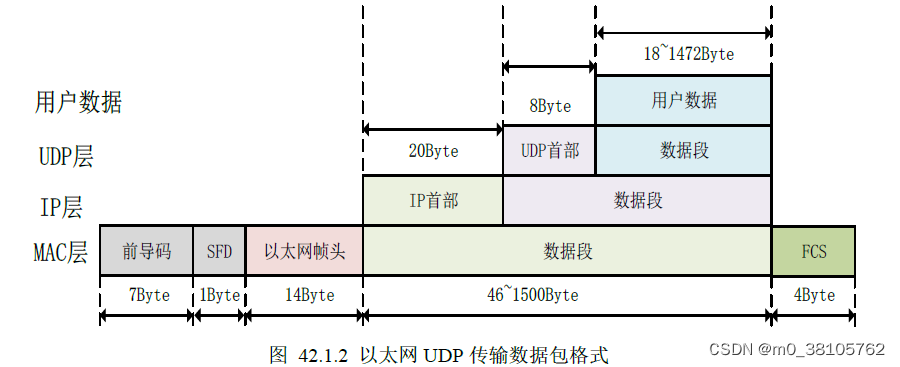

上面几个模块完成了udp+ip的协议组包,也就是UDP协议及verilog实现——(二)协议解读-CSDN博客

中提到的除了前导码、SFD、以太网帧头、FCS以外的协议均由UDP_COMPLETE模块完成了封装。

四、代码数据流分析——MAC层封装

那么MAC层的前导码、SFD、以太网帧头、FCS在哪封装呢?通过vivado工程目录可以看出,

含有ETH的模块有两个,eth_axis_tx,和eth_mac_10g_fifo。

eth_axis_tx简单一些,查看eth_axis_tx的顶层,正好与UDP_COMPLETE的ETH_FRAME out接口吻合,且查看模块中的注释文字,发现其完成的是以太网帧头的封装。

而eth_mac_10g_fifo复杂一些,因此逐层往下搜索。

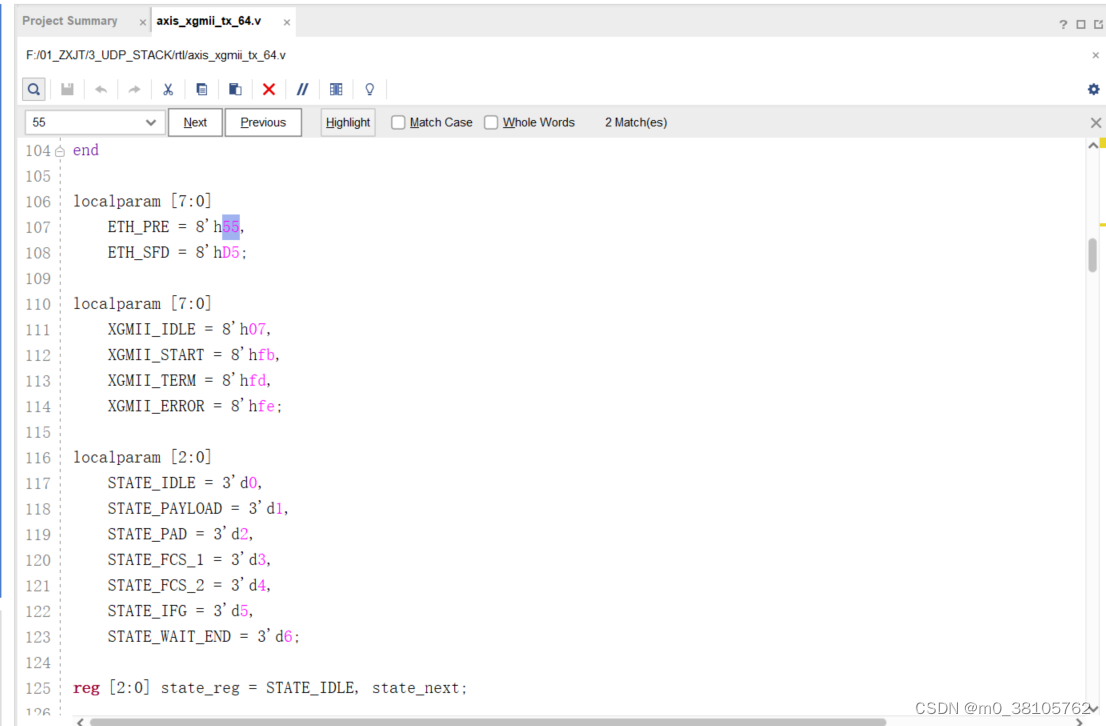

在axis_xgmii_tx_64中能看到,ETH_PRE为55,ETH_SFD为D5,就对应前导码和SFD的模块,且该模块中包含crc计算,说明也能完成FCS的计算和封装。

至此大致思路就出来了:将UDP_COMPLETE->ETH_AXIS_TX->ETH_MAC_10G_FIFO模块进行连接(在UDP_COMPLETE的UDP_INPUT接口输入用户数据,UDP_COMPLETE的Ethernet frame output接口接ETH_AXIS_TX,ETH_AXIS_TX接eth_mac_10g_fifo即可。

大致看了看eth_mac_10g_fifo的模块,再往后的输出接口应该就是给到PHY芯片的信号了,xgmii类型的信号。

以上就是大致的阅读思路,后续会继续讲下搭建仿真环境的操作。

仿真的话可以用vcs、vivado、modelsim都可以,按自己熟悉的环境搭建即可,我这边比较熟悉的就是vcs和vivado的环境,所以会到时候看哪个方便就截图说一下。

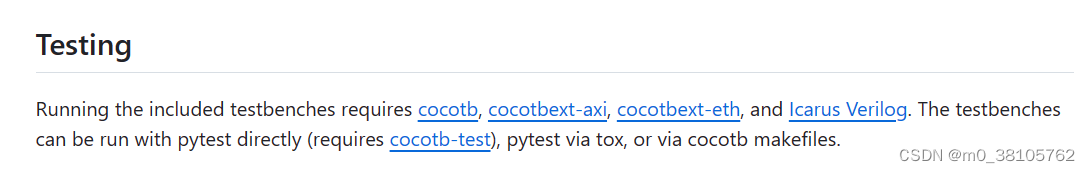

github的原创作者是用的cocotb+icarus verilog,但依赖的库较多前期花了不少功夫。最后感觉效果差不多,操作也比较陌生,所以只是简单试了试模块级的仿真。倒是挺方便,用python在windows环境就可以实现,感兴趣可以自己尝试下。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)